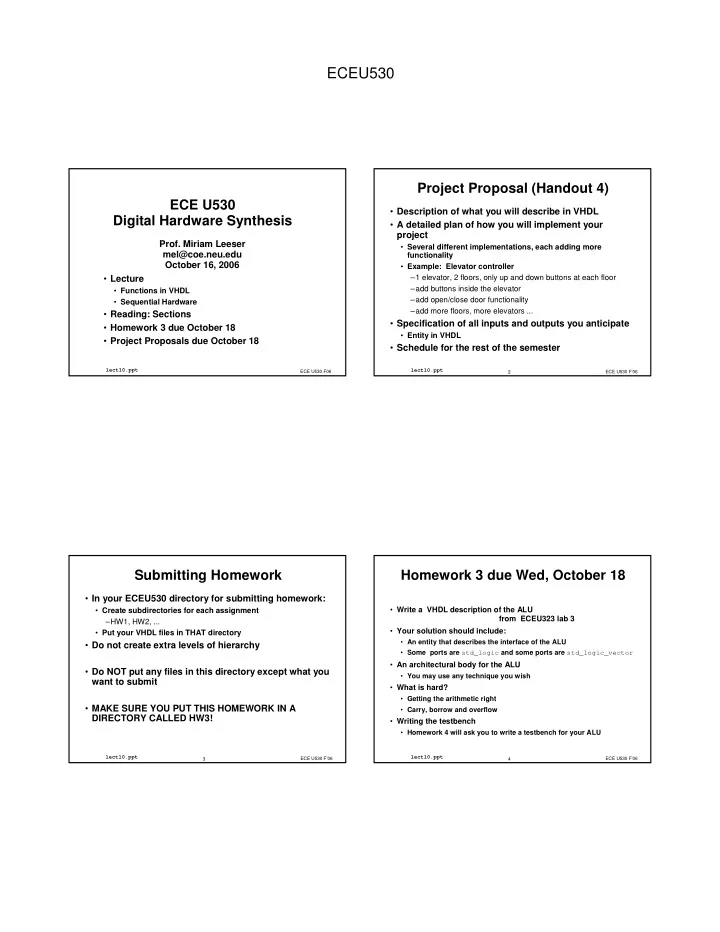

ECEU530

ECE U530 Digital Hardware Synthesis

- Lecture

- Functions in VHDL

- Sequential Hardware

- Reading: Sections

- Homework 3 due October 18

- Project Proposals due October 18

ECE U530 F06

lect10.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu October 16, 2006

ECE U530 F’06 2

lect10.ppt

Project Proposal (Handout 4)

- Description of what you will describe in VHDL

- A detailed plan of how you will implement your

project

- Several different implementations, each adding more

functionality

- Example: Elevator controller

–1 elevator, 2 floors, only up and down buttons at each floor –add buttons inside the elevator –add open/close door functionality –add more floors, more elevators ...

- Specification of all inputs and outputs you anticipate

- Entity in VHDL

- Schedule for the rest of the semester

ECE U530 F’06 3

lect10.ppt

Submitting Homework

- In your ECEU530 directory for submitting homework:

- Create subdirectories for each assignment

–HW1, HW2, ...

- Put your VHDL files in THAT directory

- Do not create extra levels of hierarchy

- Do NOT put any files in this directory except what you

want to submit

- MAKE SURE YOU PUT THIS HOMEWORK IN A

DIRECTORY CALLED HW3!

ECE U530 F’06 4

lect10.ppt

Homework 3 due Wed, October 18

- Write a VHDL description of the ALU

from ECEU323 lab 3

- Your solution should include:

- An entity that describes the interface of the ALU

- Some ports are std_logic and some ports are std_logic_vector

- An architectural body for the ALU

- You may use any technique you wish

- What is hard?

- Getting the arithmetic right

- Carry, borrow and overflow

- Writing the testbench

- Homework 4 will ask you to write a testbench for your ALU