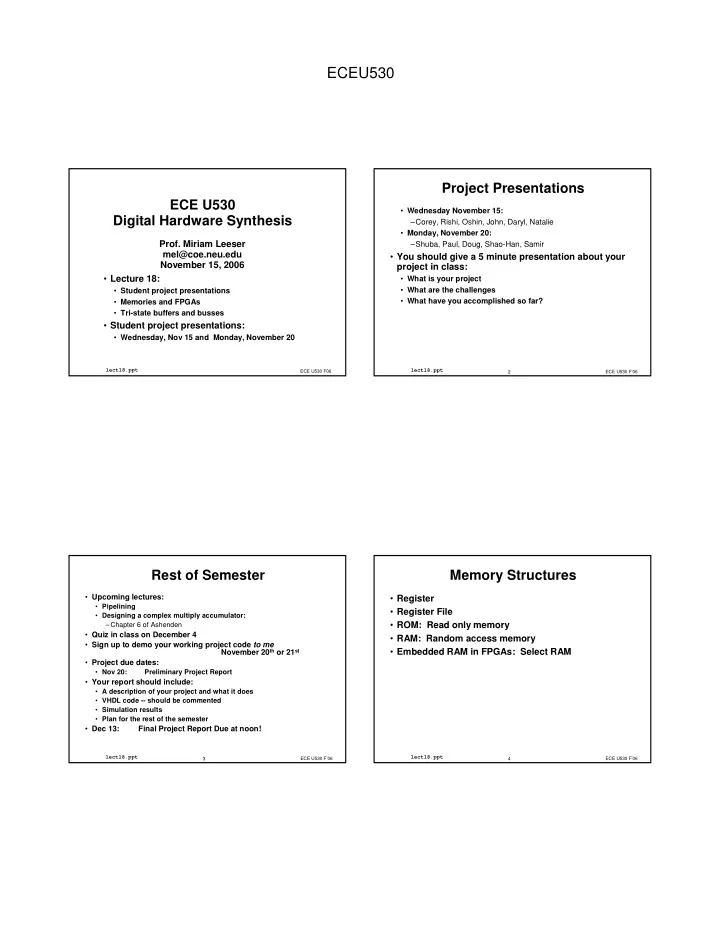

ECEU530

ECE U530 Digital Hardware Synthesis

- Lecture 18:

- Student project presentations

- Memories and FPGAs

- Tri-state buffers and busses

- Student project presentations:

- Wednesday, Nov 15 and Monday, November 20

ECE U530 F06

lect18.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu November 15, 2006

ECE U530 F’06 2

lect18.ppt

Project Presentations

- Wednesday November 15:

–Corey, Rishi, Oshin, John, Daryl, Natalie

- Monday, November 20:

–Shuba, Paul, Doug, Shao-Han, Samir

- You should give a 5 minute presentation about your

project in class:

- What is your project

- What are the challenges

- What have you accomplished so far?

ECE U530 F’06 3

lect18.ppt

Rest of Semester

- Upcoming lectures:

- Pipelining

- Designing a complex multiply accumulator:

– Chapter 6 of Ashenden

- Quiz in class on December 4

- Sign up to demo your working project code to me

November 20th or 21st

- Project due dates:

- Nov 20: Preliminary Project Report

- Your report should include:

- A description of your project and what it does

- VHDL code -- should be commented

- Simulation results

- Plan for the rest of the semester

- Dec 13: Final Project Report Due at noon!

ECE U530 F’06 4

lect18.ppt

Memory Structures

- Register

- Register File

- ROM: Read only memory

- RAM: Random access memory

- Embedded RAM in FPGAs: Select RAM