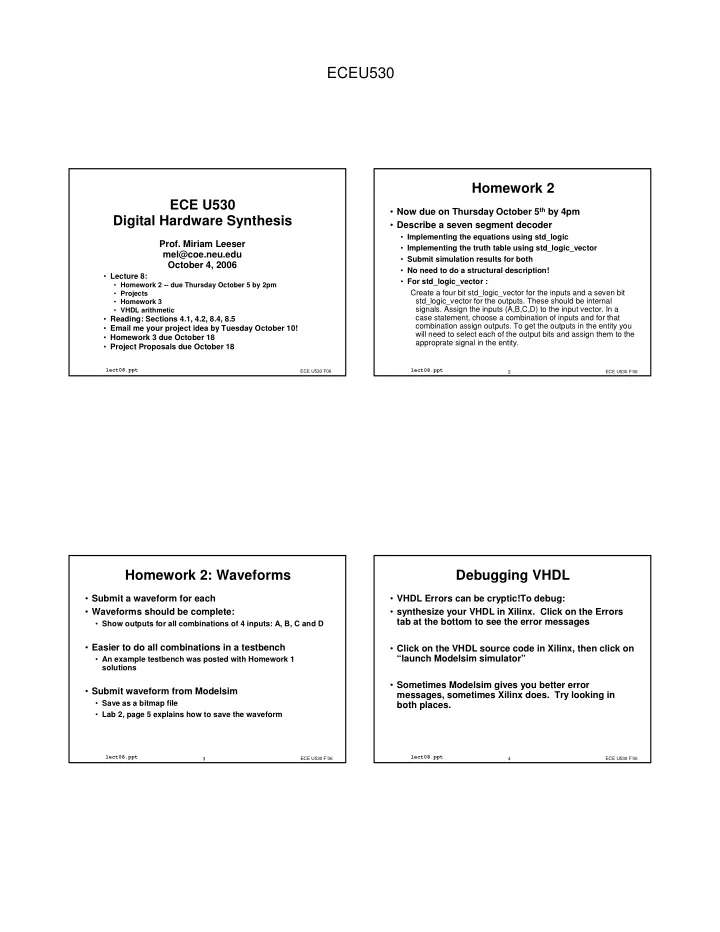

ECEU530

ECE U530 Digital Hardware Synthesis

- Lecture 8:

- Homework 2 -- due Thursday October 5 by 2pm

- Projects

- Homework 3

- VHDL arithmetic

- Reading: Sections 4.1, 4.2, 8.4, 8.5

- Email me your project idea by Tuesday October 10!

- Homework 3 due October 18

- Project Proposals due October 18

ECE U530 F06

lect08.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu October 4, 2006

ECE U530 F’06 2

lect08.ppt

Homework 2

- Now due on Thursday October 5th by 4pm

- Describe a seven segment decoder

- Implementing the equations using std_logic

- Implementing the truth table using std_logic_vector

- Submit simulation results for both

- No need to do a structural description!

- For std_logic_vector :

Create a four bit std_logic_vector for the inputs and a seven bit std_logic_vector for the outputs. These should be internal

- signals. Assign the inputs (A,B,C,D) to the input vector. In a

case statement, choose a combination of inputs and for that combination assign outputs. To get the outputs in the entity you will need to select each of the output bits and assign them to the approprate signal in the entity.

ECE U530 F’06 3

lect08.ppt

Homework 2: Waveforms

- Submit a waveform for each

- Waveforms should be complete:

- Show outputs for all combinations of 4 inputs: A, B, C and D

- Easier to do all combinations in a testbench

- An example testbench was posted with Homework 1

solutions

- Submit waveform from Modelsim

- Save as a bitmap file

- Lab 2, page 5 explains how to save the waveform

ECE U530 F’06 4

lect08.ppt

Debugging VHDL

- VHDL Errors can be cryptic!To debug:

- synthesize your VHDL in Xilinx. Click on the Errors

tab at the bottom to see the error messages

- Click on the VHDL source code in Xilinx, then click on

“launch Modelsim simulator”

- Sometimes Modelsim gives you better error