ECEU530

ECE U530 Digital Hardware Synthesis

- Classes November 6 and 8 are in 429 Dana!

- Lecture 15:

- Homework 5: Datapath

- How to write a testbench for synchronous circuits

- HW 5: Due Wednesday, November 8

- Project Progress reports due

Friday, November 10

ECE U530 F06

lect15.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu November 6, 2006

ECE U530 F’06 2

lect15.ppt

Schedule

- Classes on November 6 and 8 will be in 429 Dana

- Homework 5 due Wednesday, November 8

- Write the Datapath for the calculator from ECEU323 in VHDL

- Use the posted entity

- Project progress report due Friday, November 10:

- and email to me telling me where your project stands

- some working VHDL code in your home directory

- Homework 6: Lab 5 due Wednesday November 15

- November 15th and 20th: student presentations on

projects: sign up for a date to do your project presentation

- Sign up to demo your working project code

November 20th or 21st

ECE U530 F’06 3

lect15.ppt

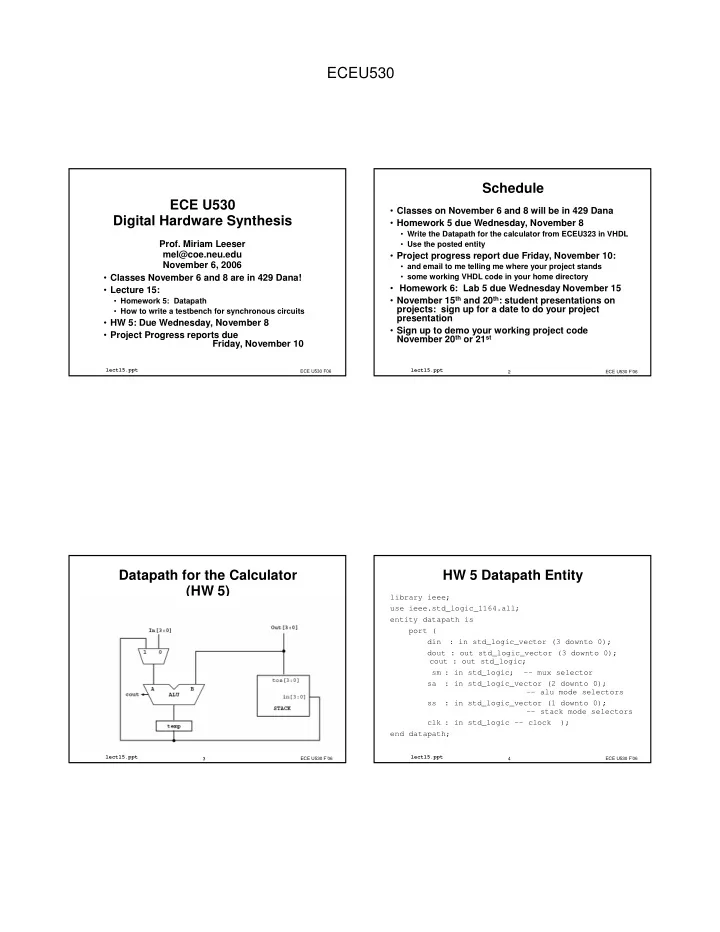

Datapath for the Calculator (HW 5)

ECE U530 F’06 4

lect15.ppt

HW 5 Datapath Entity

library ieee; use ieee.std_logic_1164.all; entity datapath is port ( din : in std_logic_vector (3 downto 0); dout : out std_logic_vector (3 downto 0); cout : out std_logic; sm : in std_logic; -- mux selector sa : in std_logic_vector (2 downto 0);

- - alu mode selectors

ss : in std_logic_vector (1 downto 0);

- - stack mode selectors