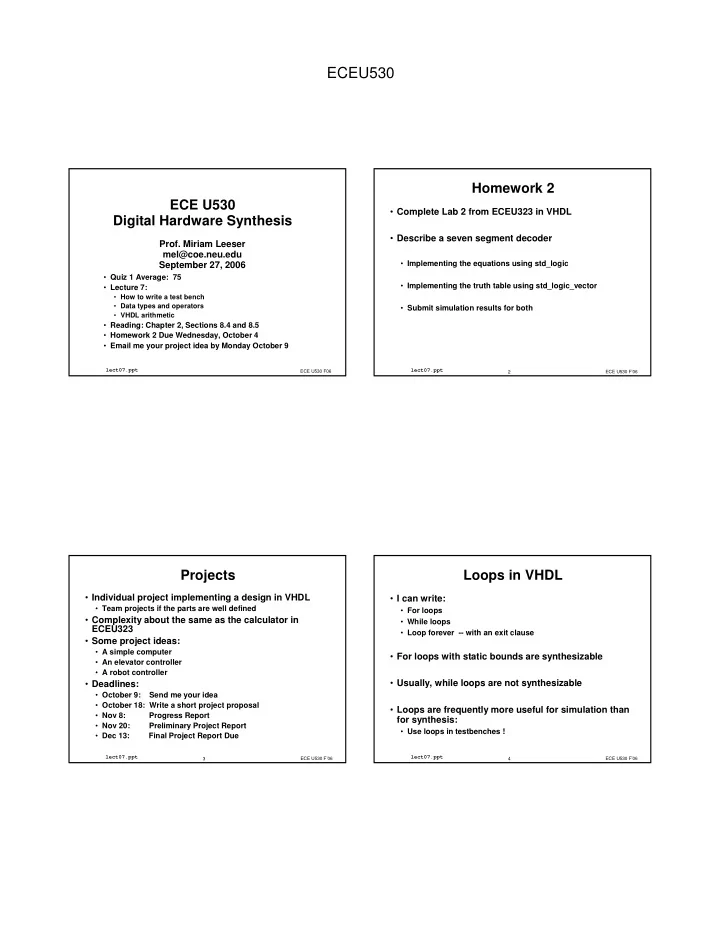

ECEU530

ECE U530 Digital Hardware Synthesis

- Quiz 1 Average: 75

- Lecture 7:

- How to write a test bench

- Data types and operators

- VHDL arithmetic

- Reading: Chapter 2, Sections 8.4 and 8.5

- Homework 2 Due Wednesday, October 4

- Email me your project idea by Monday October 9

ECE U530 F06

lect07.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu September 27, 2006

ECE U530 F’06 2

lect07.ppt

Homework 2

- Complete Lab 2 from ECEU323 in VHDL

- Describe a seven segment decoder

- Implementing the equations using std_logic

- Implementing the truth table using std_logic_vector

- Submit simulation results for both

ECE U530 F’06 3

lect07.ppt

Projects

- Individual project implementing a design in VHDL

- Team projects if the parts are well defined

- Complexity about the same as the calculator in

ECEU323

- Some project ideas:

- A simple computer

- An elevator controller

- A robot controller

- Deadlines:

- October 9: Send me your idea

- October 18: Write a short project proposal

- Nov 8: Progress Report

- Nov 20: Preliminary Project Report

- Dec 13: Final Project Report Due

ECE U530 F’06 4

lect07.ppt

Loops in VHDL

- I can write:

- For loops

- While loops

- Loop forever -- with an exit clause

- For loops with static bounds are synthesizable

- Usually, while loops are not synthesizable

- Loops are frequently more useful for simulation than

for synthesis:

- Use loops in testbenches !