ECEU530

ECE U530 Digital Hardware Synthesis

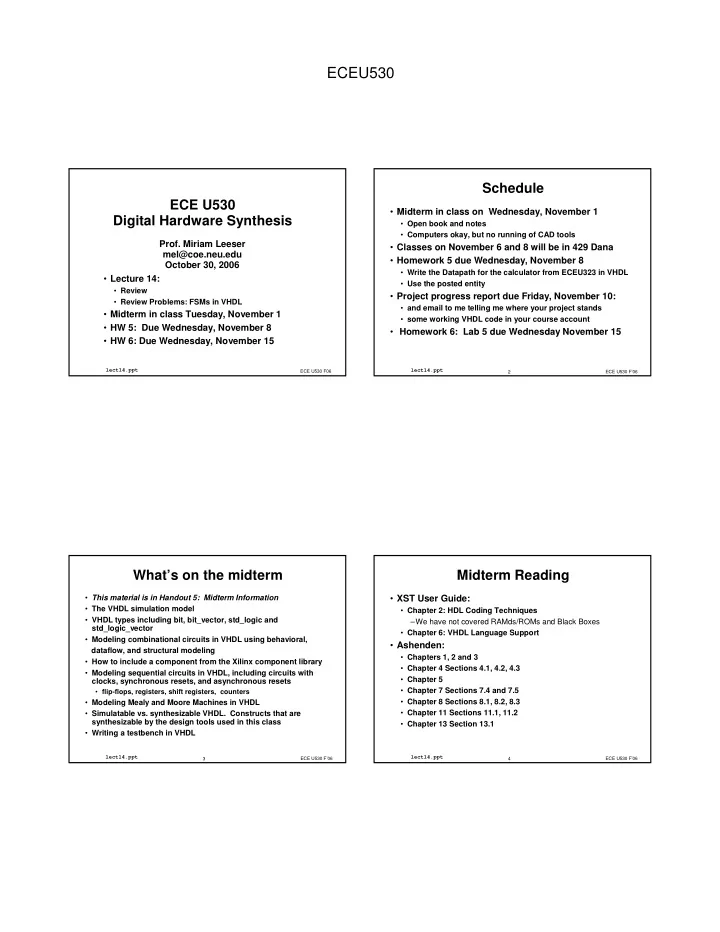

- Lecture 14:

- Review

- Review Problems: FSMs in VHDL

- Midterm in class Tuesday, November 1

- HW 5: Due Wednesday, November 8

- HW 6: Due Wednesday, November 15

ECE U530 F06

lect14.ppt

- Prof. Miriam Leeser

mel@coe.neu.edu October 30, 2006

ECE U530 F’06 2

lect14.ppt

Schedule

- Midterm in class on Wednesday, November 1

- Open book and notes

- Computers okay, but no running of CAD tools

- Classes on November 6 and 8 will be in 429 Dana

- Homework 5 due Wednesday, November 8

- Write the Datapath for the calculator from ECEU323 in VHDL

- Use the posted entity

- Project progress report due Friday, November 10:

- and email to me telling me where your project stands

- some working VHDL code in your course account

- Homework 6: Lab 5 due Wednesday November 15

ECE U530 F’06 3

lect14.ppt

What’s on the midterm

- This material is in Handout 5: Midterm Information

- The VHDL simulation model

- VHDL types including bit, bit_vector, std_logic and

std_logic_vector

- Modeling combinational circuits in VHDL using behavioral,

dataflow, and structural modeling

- How to include a component from the Xilinx component library

- Modeling sequential circuits in VHDL, including circuits with

clocks, synchronous resets, and asynchronous resets

- flip-flops, registers, shift registers, counters

- Modeling Mealy and Moore Machines in VHDL

- Simulatable vs. synthesizable VHDL. Constructs that are

synthesizable by the design tools used in this class

- Writing a testbench in VHDL

ECE U530 F’06 4

lect14.ppt

Midterm Reading

- XST User Guide:

- Chapter 2: HDL Coding Techniques

–We have not covered RAMds/ROMs and Black Boxes

- Chapter 6: VHDL Language Support

- Ashenden:

- Chapters 1, 2 and 3

- Chapter 4 Sections 4.1, 4.2, 4.3

- Chapter 5

- Chapter 7 Sections 7.4 and 7.5

- Chapter 8 Sections 8.1, 8.2, 8.3

- Chapter 11 Sections 11.1, 11.2

- Chapter 13 Section 13.1