Read Only Memory ROM

William Sandqvist william@kth.se

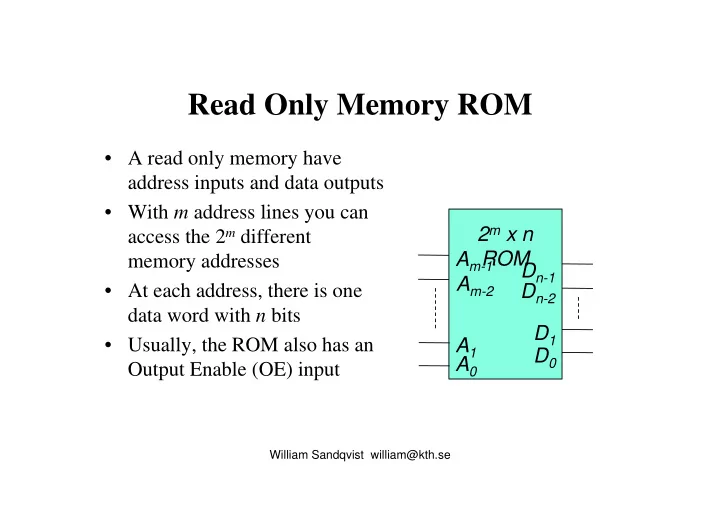

Am-1 Am-2 A0 A1 2m x n ROM Dn-1 Dn-2 D1 D0

- A read only memory have

address inputs and data outputs

- With m address lines you can

access the 2m different memory addresses

- At each address, there is one

data word with n bits

- Usually, the ROM also has an