dt10 2011 4.1

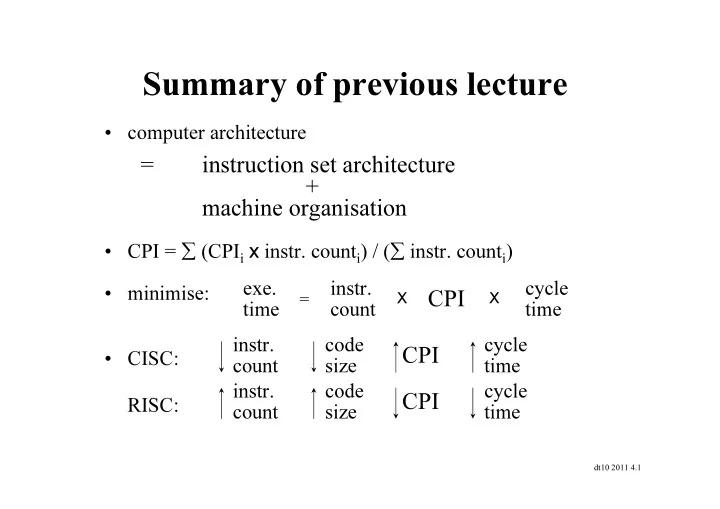

Summary of previous lecture

- computer architecture

- CPI = ∑ (CPIi x instr. counti) / (∑ instr. counti)

- minimise:

- CISC:

RISC:

= instruction set architecture + machine organisation

exe. time instr. count cycle time

CPI

X X

Summary of previous lecture computer architecture = instruction - - PowerPoint PPT Presentation

Summary of previous lecture computer architecture = instruction set architecture + machine organisation CPI = (CPI i x instr. count i ) / ( instr. count i ) exe. instr. cycle minimise: X CPI X = time count time

dt10 2011 4.1

X X

dt10 2011 4.2

(3rd Ed: p.160-175, Apx. B; 4th Ed: p.87-94, p.224-229, Apx. C.5)

dt10 2011 4.3

20 bits introduce zeros

16 10 8 R type funct source2 dest. shamt source1

dt10 2011 4.4

dt10 2011 4.5

dt10 2011 4.6

dt10 2011 4.7

dt10 2011 4.8

dt10 2011 4.9

dt10 2011 4.10

dt10 2011 4.11

dt10 2011 4.12

dt10 2011 4.13

(3rd Ed: p.250-274, 4th Ed: p.230-242)

dt10 2011 4.14

dt10 2011 4.15

The multiplicand register, ALU, and Product register are all 64 bits wide, with only the Multiplier register containing 32 bits. The 32-bit multiplicand starts in the right half of the Multiplicand register, and is shifted left 1 bit on each

to 0. Control decides when to shift the Multiplicand and Multiplier registers and when to write new values into the Product register.

dt10 2011 4.16

dt10 2011 4.17

The Multiplicand register, ALU, and Multiplier register are all 32 bits wide, with only the Product register left as 64 bits. Now the product is shifted right.

dt10 2011 4.18

LH: left Half

dt10 2011 4.19

m = 00100 k = 2

dt10 2011 4.20

dt10 2011 4.21

1001 q ds 1000 1001010 dd (r ´ : intermediate value)

align MSB(ds) and MSB(dd) 0010 r ´< ds: q = q ++ <0> 0101 1010 ← r ´≥ ds: q = q ++ <1>

10 r (r = r ´ when finished)

dt10 2011 4.22

loop: r = r - ds if r ≥ 0 left shift q, LSB(q)=1 else r = r + ds, left shift (q) LSB(q) = 0 right shift ds

The Divisor register, ALU, and Remainder register are all 64 bits wide, with only the Quotient register being 32 bits. The 32-bit divisor starts in the left half of the Divisor register and is shifted right 1 bit on each step. The remainder is initialised with the dividend. Control decides when to shift the Divisor and Quotient registers and when to write the new value into the Remainder register.

dt10 2011 4.23

dt10 2011 4.24