Slides for Lecture 16

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

11 March, 2014

ENCM 501 W14 Slides for Lecture 16

slide 2/26

Previous Lecture

◮ context switches and effects on memory latency ◮ memory system summary ◮ introduction to ILP (instruction-level parallelism) ◮ review of simple pipelining

ENCM 501 W14 Slides for Lecture 16

slide 3/26

Today’s Lecture

◮ pipeline hazards ◮ solutions to pipeline hazards

Related reading in Hennessy & Patterson: Sections C.2–C.3

ENCM 501 W14 Slides for Lecture 16

slide 4/26

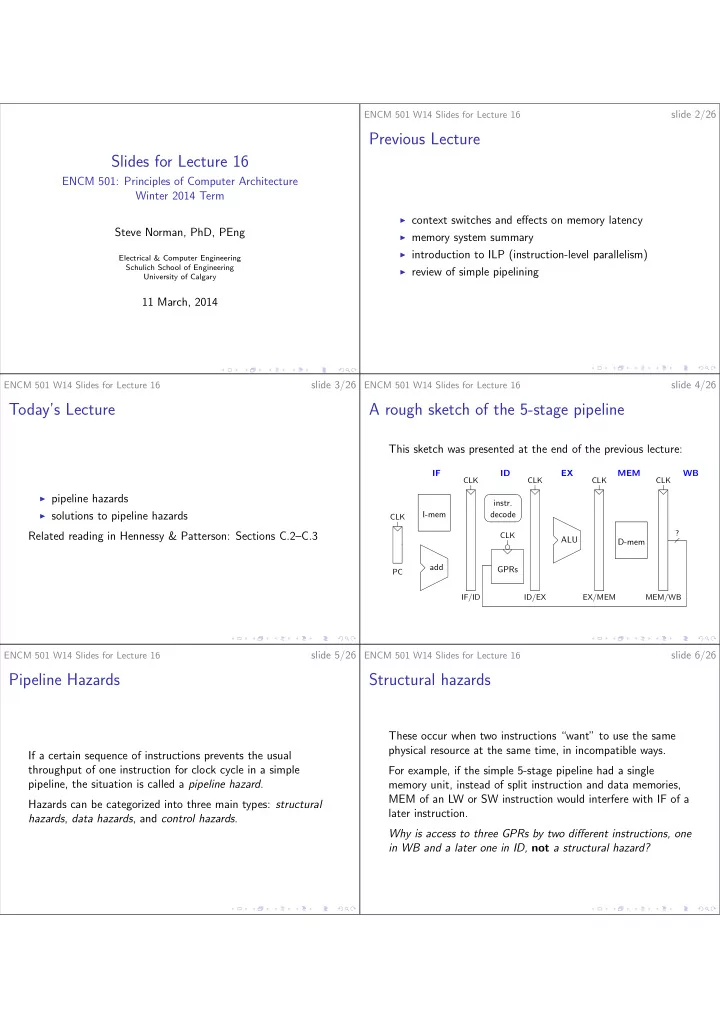

A rough sketch of the 5-stage pipeline

This sketch was presented at the end of the previous lecture:

CLK IF/ID CLK ID/EX CLK EX/MEM CLK MEM/WB

GPRs I-mem D-mem instr. decode add ID IF EX MEM WB ALU

? CLK PC CLK