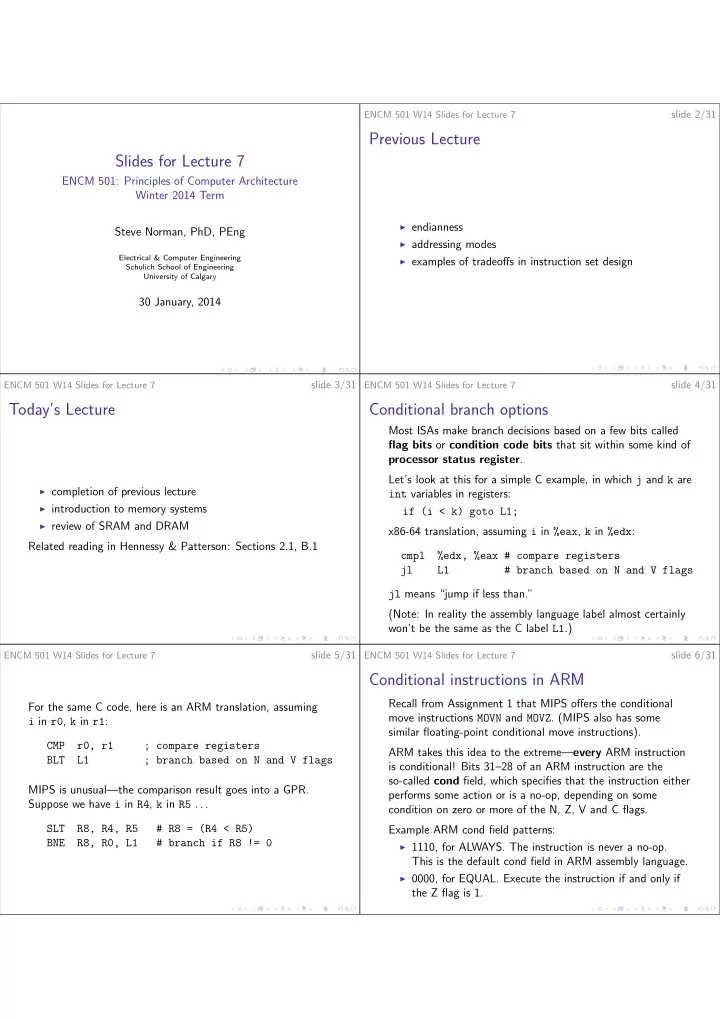

Slides for Lecture 7

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

30 January, 2014

ENCM 501 W14 Slides for Lecture 7

slide 2/31

Previous Lecture

◮ endianness ◮ addressing modes ◮ examples of tradeoffs in instruction set design

ENCM 501 W14 Slides for Lecture 7

slide 3/31

Today’s Lecture

◮ completion of previous lecture ◮ introduction to memory systems ◮ review of SRAM and DRAM

Related reading in Hennessy & Patterson: Sections 2.1, B.1

ENCM 501 W14 Slides for Lecture 7

slide 4/31

Conditional branch options

Most ISAs make branch decisions based on a few bits called flag bits or condition code bits that sit within some kind of processor status register. Let’s look at this for a simple C example, in which j and k are int variables in registers: if (i < k) goto L1; x86-64 translation, assuming i in %eax, k in %edx: cmpl %edx, %eax # compare registers jl L1 # branch based on N and V flags jl means “jump if less than.” (Note: In reality the assembly language label almost certainly won’t be the same as the C label L1.)

ENCM 501 W14 Slides for Lecture 7

slide 5/31

For the same C code, here is an ARM translation, assuming i in r0, k in r1: CMP r0, r1 ; compare registers BLT L1 ; branch based on N and V flags MIPS is unusual—the comparison result goes into a GPR. Suppose we have i in R4, k in R5 . . . SLT R8, R4, R5 # R8 = (R4 < R5) BNE R8, R0, L1 # branch if R8 != 0

ENCM 501 W14 Slides for Lecture 7

slide 6/31

Conditional instructions in ARM

Recall from Assignment 1 that MIPS offers the conditional move instructions MOVN and MOVZ. (MIPS also has some similar floating-point conditional move instructions). ARM takes this idea to the extreme—every ARM instruction is conditional! Bits 31–28 of an ARM instruction are the so-called cond field, which specifies that the instruction either performs some action or is a no-op, depending on some condition on zero or more of the N, Z, V and C flags. Example ARM cond field patterns:

◮ 1110, for ALWAYS. The instruction is never a no-op.

This is the default cond field in ARM assembly language.

◮ 0000, for EQUAL. Execute the instruction if and only if