Slides for Lecture 23

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

3 April, 2014

ENCM 501 W14 Slides for Lecture 23

slide 2/19

Previous Lecture

◮ introduction to cache coherency protocols

ENCM 501 W14 Slides for Lecture 23

slide 3/19

Today’s Lecture

◮ MSI protocol for cache concurrency ◮ snooping to support MSI and similar protocols ◮ race conditions at ILP and TLP levels ◮ use of locks to manage TLP races ◮ introduction to ISA support for locks

Related reading in Hennessy & Patterson: Sections 5.2, 5.5

ENCM 501 W14 Slides for Lecture 23

slide 4/19

Quick review: Caches in multi-core systems

These points were made in the previous lecture:

◮ In a writeback cache in a uniprocessor (one-core,

no SMT) system, possible states of a cache block are invalid, clean, or dirty.

◮ For that writeback cache in a uniprocessor system, block

states usually change as a result of loads and stores processed within the single core. (Messy detail: Actions such as DMA by I/O devices can also change states of blocks.)

◮ In a multicore system, one of many possible choices for

sets of possible cache block states is MSI: modified, shared, or invalid. State changes in a cache in one core may be triggered by actions in another core.

ENCM 501 W14 Slides for Lecture 23

slide 5/19

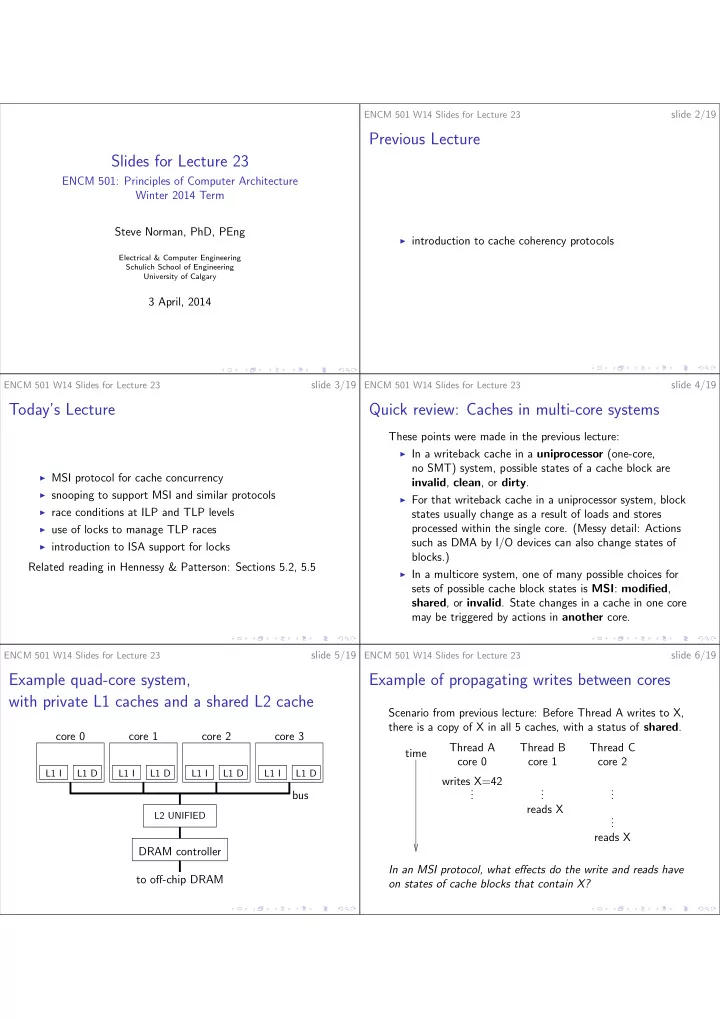

Example quad-core system, with private L1 caches and a shared L2 cache

L1 I L1 D

core 0

L1 I L1 D

core 1

L1 I L1 D

core 2

L1 I L1 D

core 3 bus

L2 UNIFIED

DRAM controller to off-chip DRAM

ENCM 501 W14 Slides for Lecture 23

slide 6/19

Example of propagating writes between cores

Scenario from previous lecture: Before Thread A writes to X, there is a copy of X in all 5 caches, with a status of shared. Thread A core 0 Thread C core 2 Thread B core 1 time writes X=42 . . . . . . reads X . . . reads X . . . In an MSI protocol, what effects do the write and reads have

- n states of cache blocks that contain X?