Lecture 12

Logistics

HW4 was due yesterday HW5 was out yesterday (due next Wednesday) HW5 was out yesterday (due next Wednesday) Feedback: thank you! Things to work on: Big picture, Book chapters, Exam comments

Last lecture

Adders

Today

Cl ifi ti f Add

1

CSE370, Lecture 13 Clarification of Adders Summary of Combinational Logic Introduction to Sequential Logic

The basic concepts A simple example

12

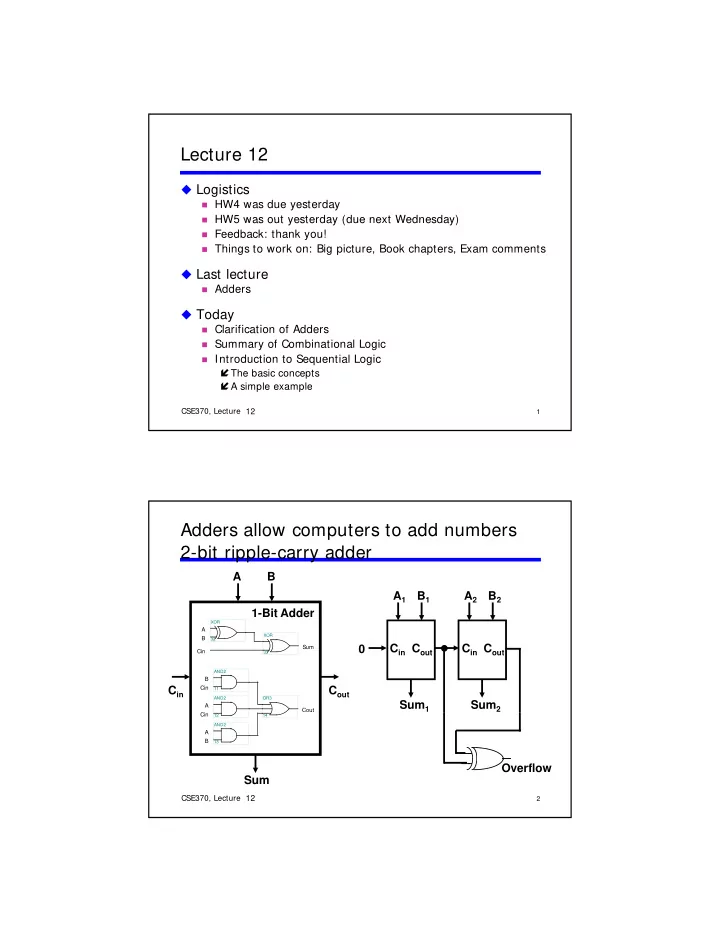

Adders allow computers to add numbers 2-bit ripple-carry adder

A1 B1 A B A2 B2 Cout Cin Sum1

Ci A Cout Cin B

AND2 OR3 11 AND2

Cin Sum B A

33 XOR 32 XOR

Cout Cin 1-Bit Adder Sum2 Cout Cin

2

CSE370, Lecture 13

A B Cin

13 AND2 12 14

Sum Overflow

11 12