1

Introduction to CMOS VLSI Design

Lecture 11: Adders

David Harris

Harvey Mudd College Spring 2004

11: Adders Slide 2 CMOS VLSI Design

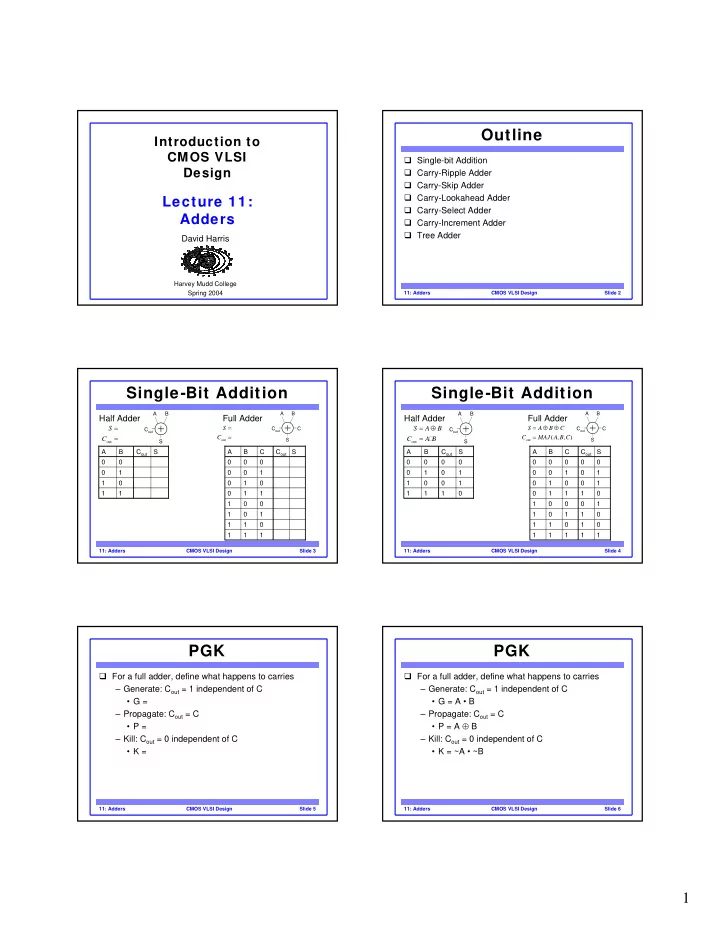

Outline

Single-bit Addition Carry-Ripple Adder Carry-Skip Adder Carry-Lookahead Adder Carry-Select Adder Carry-Increment Adder Tree Adder

11: Adders Slide 3 CMOS VLSI Design

Single-Bit Addition

Half Adder Full Adder

1 1 1 1 S Cout B A 1 1 1 1 1 1 1 1 1 1 1 1 S Cout C B A

A B S Cout A B C S Cout

- ut

S C = =

- ut

S C = =

11: Adders Slide 4 CMOS VLSI Design

Single-Bit Addition

Half Adder Full Adder

1 1 1 1 1 1 1 S Cout B A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 S Cout C B A

A B S Cout A B C S Cout

- ut

S A B C A B = ⊕ =

- ut

( , , ) S A B C C MAJ A B C = ⊕ ⊕ =

11: Adders Slide 5 CMOS VLSI Design

PGK

For a full adder, define what happens to carries – Generate: Cout = 1 independent of C

- G =

– Propagate: Cout = C

- P =

– Kill: Cout = 0 independent of C

- K =

11: Adders Slide 6 CMOS VLSI Design

PGK

For a full adder, define what happens to carries – Generate: Cout = 1 independent of C

- G = A • B

– Propagate: Cout = C

- P = A ⊕ B

– Kill: Cout = 0 independent of C

- K = ~A • ~B