SLIDE 1

Figure5.2 Half-adder x i y i c 00 01 11 10 i 1 1 0 c i x - - PDF document

Figure5.2 Half-adder x i y i c 00 01 11 10 i 1 1 0 c i x - - PDF document

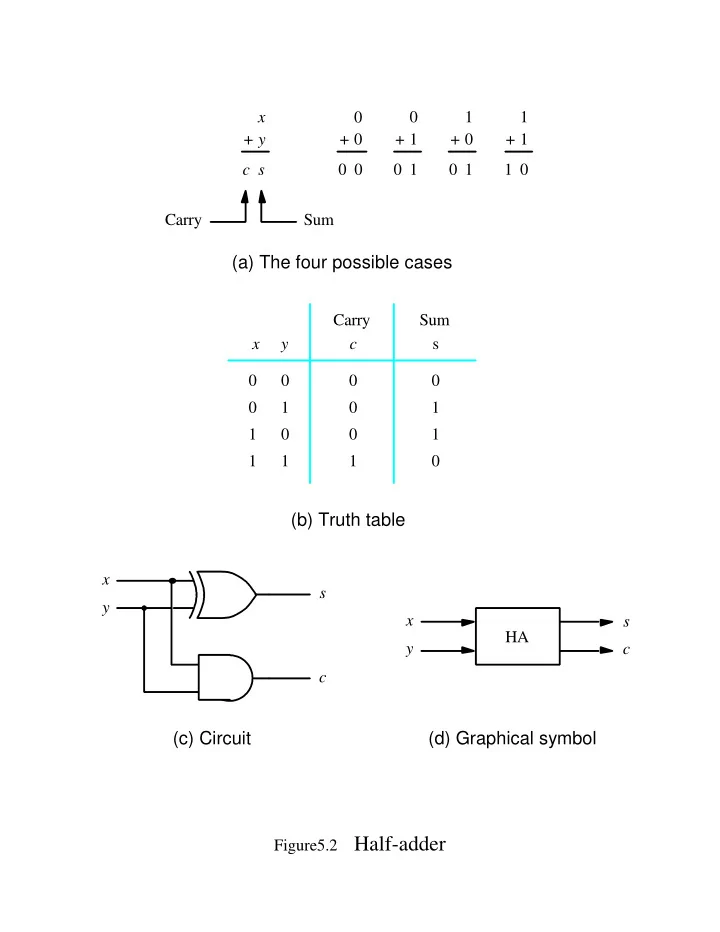

x 0 0 1 1 + y + 0 + 1 + 0 + 1 c s 0 0 0 1 0 1 1 0 Carry Sum (a) The four possible cases Carry Sum x y c s 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 (b) Truth table x s y x s HA y c c (c) Circuit (d)

SLIDE 2

SLIDE 3

Figure5.7 Circuit that multiplies an 8-bit unsigned number by 3

7

x y

7

y x

7

x y

8

y y

7

x

8

s s

7

c

7

s s

8

c

8

P

9

P

8

P P 3 A = : x

1 x

y

8

y y

7

x

8

s s

8

c

8

a

7

A : P

9

P

8

P P 3 A = :

(a) Naive approach (b) Efficient design

a a

7

A : a x

SLIDE 4

Figure5.32 Multiplication of unsigned numbers

× 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 0 0 0 0 0 1 1 1 0 1 0 0 1 1 0 1 0 Multiplicand M Multiplier Q Product P (14) (11) (154) × 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 0 1 0 0 1 1 0 1 0 Multiplicand M Multiplier Q Product P (11) (14) (154) + 1 0 1 0 1 0 0 0 0 + 0 1 0 1 0 1 1 1 0 + Partial product 0 Partial product 1 Partial product 2 (a) Multiplication by hand (b) Multiplication for implementation in hardware

SLIDE 5

Figure5.33 A 4 x 4 multiplier circuit

p

7

p

6

p

5

p

4

p

3

p

2

p

1

p q

2

q

1

q

3

q m

3

m

2

m

1

m PP1 PP2

(a) Structure of the circuit

m

k

q j c

in

Bit of PPi FA c

- ut

(c) A block in the bottom two rows

m

k

q

1

c

in

FA c

- ut

(b) A block in the top row

q m

k 1 +

SLIDE 6

Figure5.34 Multiplication of signed numbers

0 0 0 1 1 1 0 0 1 1 1 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 0 1 0 1 0 0 0 0 0 0 Multiplicand M Multiplier Q Product P (+14) (+11) (+154) + + 0 0 0 1 0 1 0 0 0 1 1 1 0 + 0 0 1 0 0 1 1 0 0 0 0 0 0 + 0 0 1 0 0 1 1 0 1 0 Partial product 0 Partial product 1 Partial product 2 Partial product 3

×

1 1 1 0 0 1 0 1 0 0 1 0 0 1 0 1 1 1 1 0 0 1 0 1 1 0 1 0 1 1 0 0 0 0 0 0 Multiplicand M Multiplier Q Product P ( 14) (+11) ( 154) + + 1 1 1 0 1 0 1 1 1 0 0 1 0 + 1 1 0 1 1 0 0 0 0 0 0 0 0 + 1 1 0 1 1 0 0 1 1 0 Partial product 0 Partial product 1 Partial product 2 Partial product 3 – –

(a) Positive multiplicand (b) Negative multiplicand

x

SLIDE 7