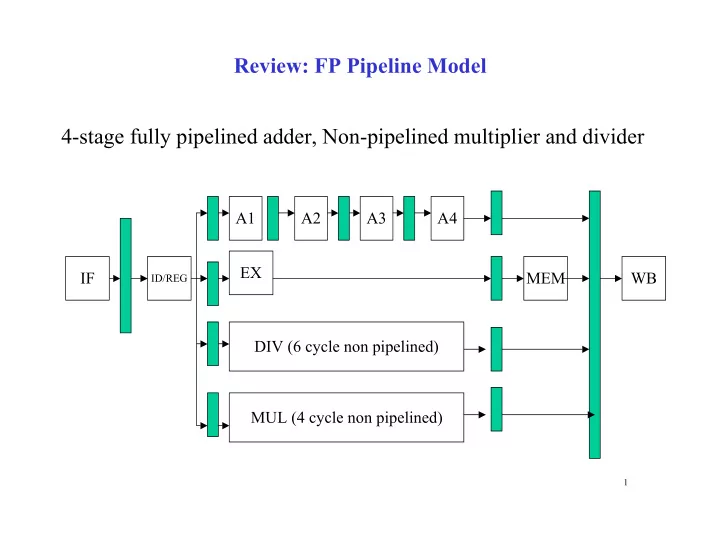

Review: FP Pipeline Model 4-stage fully pipelined adder, Non-pipelined multiplier and divider

IF

ID/REG

A1 MUL (4 cycle non pipelined) DIV (6 cycle non pipelined) EX A2 A3 A4 MEM WB

1

Review: FP Pipeline Model 4-stage fully pipelined adder, - - PowerPoint PPT Presentation

Review: FP Pipeline Model 4-stage fully pipelined adder, Non-pipelined multiplier and divider A1 A2 A3 A4 EX IF MEM WB ID/REG DIV (6 cycle non pipelined) MUL (4 cycle non pipelined) 1 Review: Summary If instructions A and B are

1

2

3

A

4

3

S D D I V

1

M U L

A

5

A

6

7

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

8

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

9

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

10

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

11

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

12

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

13

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

14

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

15

17

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

18

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

19

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

20

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

21

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

22

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

23

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

24

B A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14

25

A: DIVD F0, F2, F4 B: ADDD F10, F0, F8 C: MULTD F12, F8, F14 B

26

27

28

29

30

31

32