Slides for Lecture 8

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

4 February, 2014

ENCM 501 W14 Slides for Lecture 8

slide 2/29

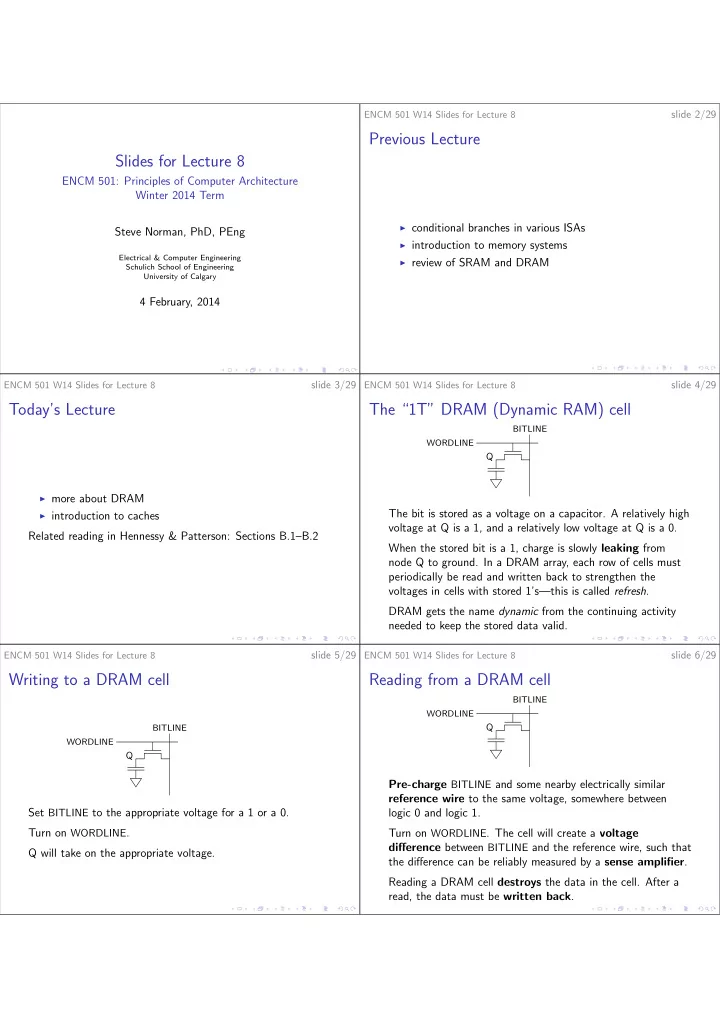

Previous Lecture

◮ conditional branches in various ISAs ◮ introduction to memory systems ◮ review of SRAM and DRAM

ENCM 501 W14 Slides for Lecture 8

slide 3/29

Today’s Lecture

◮ more about DRAM ◮ introduction to caches