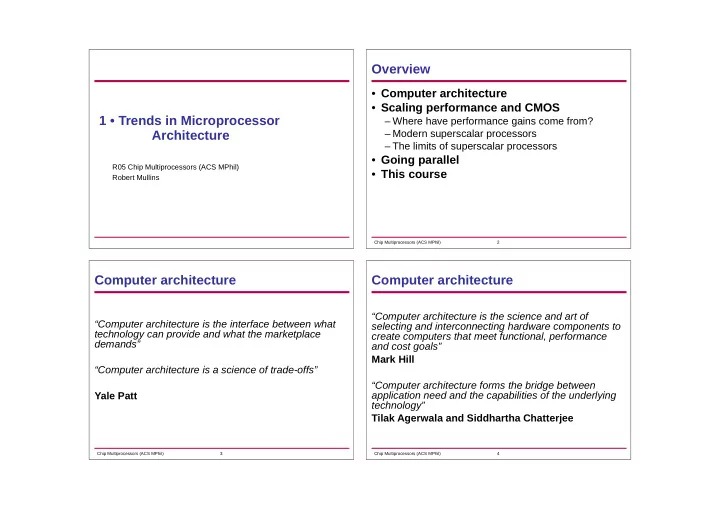

1 • Trends in Microprocessor Architecture

R05 Chip Multiprocessors (ACS MPhil) Robert Mullins

Chip Multiprocessors (ACS MPhil) 2

Overview

- Computer architecture

- Scaling performance and CMOS

– Where have performance gains come from? – Modern superscalar processors – The limits of superscalar processors

- Going parallel

- This course

Chip Multiprocessors (ACS MPhil) 3

Computer architecture

“Computer architecture is the interface between what technology can provide and what the marketplace demands” “Computer architecture is a science of trade-offs” Yale Patt

Chip Multiprocessors (ACS MPhil) 4