Chapter 5

CSc 314 · T W Bennet · Mississippi College

1

State

- Combinational Elements: Adder

- State Elements: Storage

CSc 314 · T W Bennet · Mississippi College

2

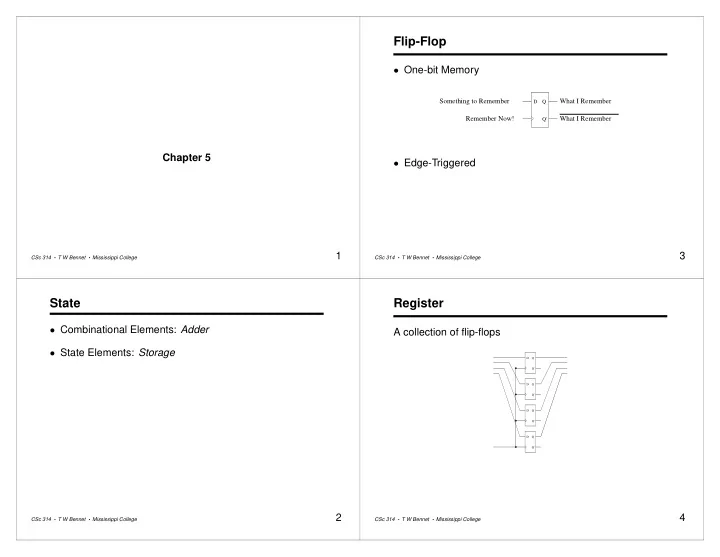

Flip-Flop

- One-bit Memory

Something to Remember What I Remember What I Remember Remember Now!

Q Q’ D

- Edge-Triggered

CSc 314 · T W Bennet · Mississippi College

3

Register

A collection of flip-flops

Q Q’ D Q Q’ D Q Q’ D Q Q’ D

CSc 314 · T W Bennet · Mississippi College