Flip-Flops

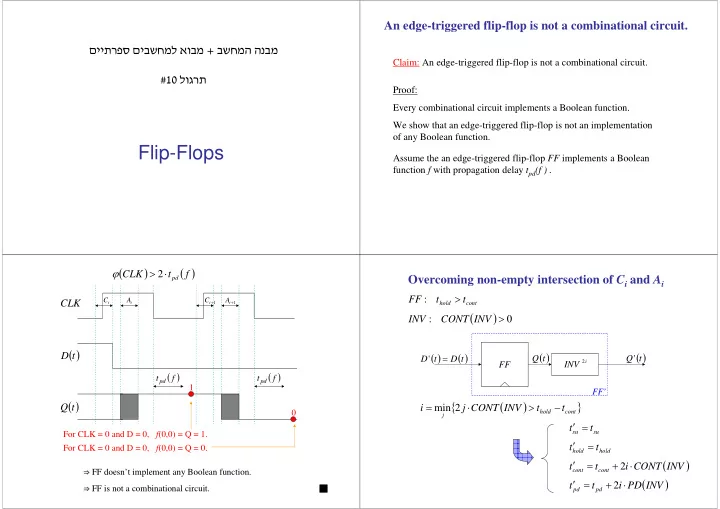

- An edge-triggered flip-flop is not a combinational circuit.

Proof: Every combinational circuit implements a Boolean function. We show that an edge-triggered flip-flop is not an implementation

- f any Boolean function.

Assume the an edge-triggered flip-flop FF implements a Boolean function f with propagation delay tpd(f ) . Claim: An edge-triggered flip-flop is not a combinational circuit.

- f

t CLK

pd

- 2

- For CLK = 0 and D = 0, f(0,0) = Q = 1.

For CLK = 0 and D = 0, f(0,0) = Q = 0.

i

C

i

A

1

- i

C

1

- i

A

f t pd 1

CLK t D t Q

- FF doesn’t implement any Boolean function.

- FF is not a combinational circuit.

f t pd

FF

i

INV 2 FF’ t D t D

- '

t Q' t Q

Overcoming non-empty intersection of Ci and Ai

cont hold

t t FF

- :

- :

- INV

CONT INV

- cont

hold j

t t INV CONT j i

- 2

min

su su

t t

- hold

hold

t t

- INV

CONT i t t

cont cont

- 2

- INV

PD i t t

pd pd

- 2