1

14:332:231 DIGITAL LOGIC DESIGN

Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013

Lecture #3: Addition, Subtraction, Multiplication, and Division

2 of 15

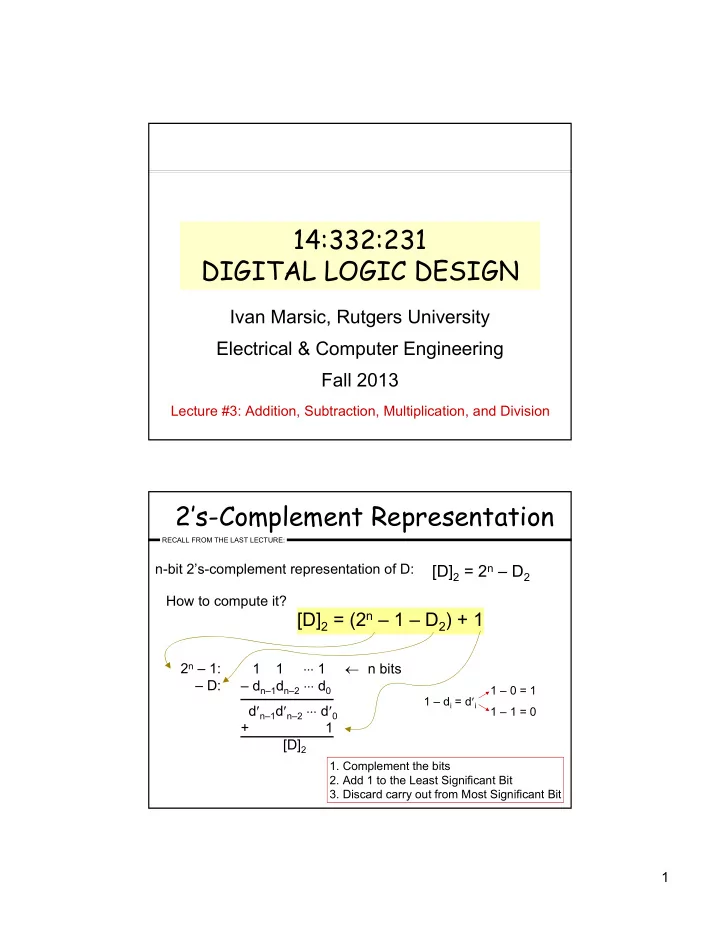

2’s-Complement Representation

n-bit 2’s-complement representation of D: How to compute it?

[D]2 = 2n – D2

- 1. Complement the bits

- 2. Add 1 to the Least Significant Bit

- 3. Discard carry out from Most Significant Bit

[D]2 = (2n – 1 – D2) + 1

2n – 1: – D: 1 1 1 n bits – dn–1dn–2 d0 dn–1dn–2 d0 + 1 [D]2

1 – di = di 1 – 0 = 1 1 – 1 = 0

RECALL FROM THE LAST LECTURE: