Slides for Lecture 6

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

28 January, 2014

ENCM 501 W14 Slides for Lecture 6

slide 2/33

Previous Lecture

◮ introduction to ISA design ideas ◮ memory-register and load-store architectures ◮ a very brief history of RISC versus CISC ◮ aspects of the ISA view of memory—flat address spaces,

alignment rules

ENCM 501 W14 Slides for Lecture 6

slide 3/33

Today’s Lecture

◮ endianness ◮ addressing modes ◮ examples of tradeoffs in instruction set design

Related reading in Hennessy & Patterson: Sections A.3–A.7

ENCM 501 W14 Slides for Lecture 6

slide 4/33

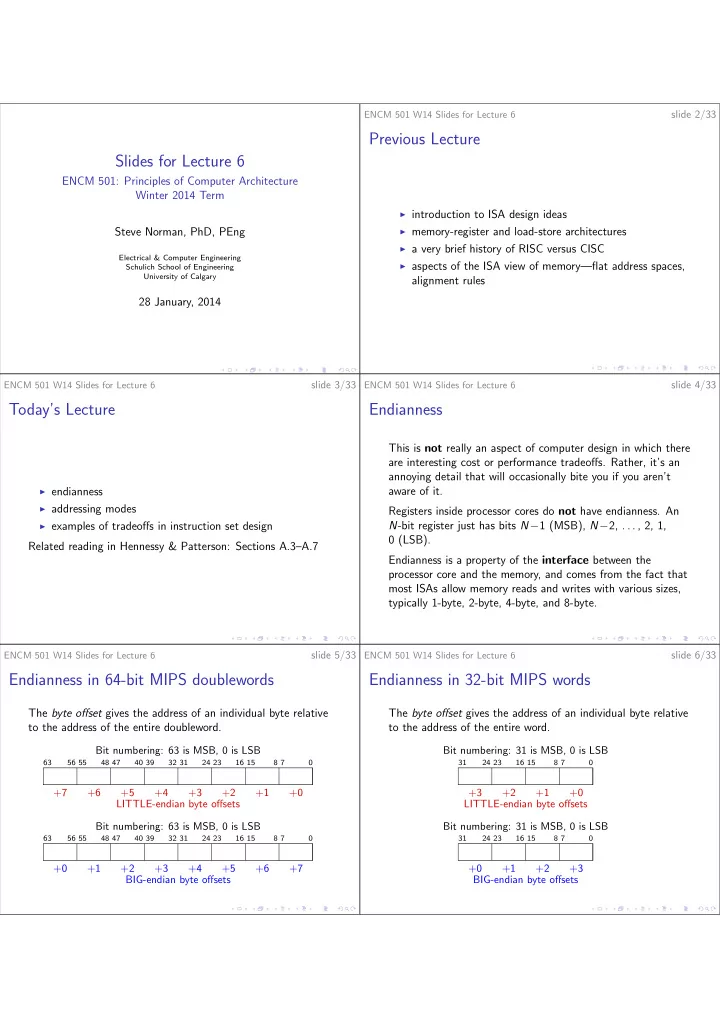

Endianness

This is not really an aspect of computer design in which there are interesting cost or performance tradeoffs. Rather, it’s an annoying detail that will occasionally bite you if you aren’t aware of it. Registers inside processor cores do not have endianness. An N-bit register just has bits N−1 (MSB), N−2, . . . , 2, 1, 0 (LSB). Endianness is a property of the interface between the processor core and the memory, and comes from the fact that most ISAs allow memory reads and writes with various sizes, typically 1-byte, 2-byte, 4-byte, and 8-byte.

ENCM 501 W14 Slides for Lecture 6

slide 5/33

Endianness in 64-bit MIPS doublewords

The byte offset gives the address of an individual byte relative to the address of the entire doubleword.

+7 +6 +5 +4 +3 +2 +1 +0

63 56 55

Bit numbering: 63 is MSB, 0 is LSB

48 47 40 39 32 31 24 23 16 15 8 7

LITTLE-endian byte offsets

63 56 55

Bit numbering: 63 is MSB, 0 is LSB

48 47 40 39 32 31 24 23 16 15 8 7

BIG-endian byte offsets +0 +1 +2 +3 +4 +5 +6 +7

ENCM 501 W14 Slides for Lecture 6

slide 6/33

Endianness in 32-bit MIPS words

The byte offset gives the address of an individual byte relative to the address of the entire word.

24 23 16 15 8 7 24 23 16 15 8 7

+3 +2 +1 +0 Bit numbering: 31 is MSB, 0 is LSB

31

LITTLE-endian byte offsets +0 +1 +2 +3 BIG-endian byte offsets Bit numbering: 31 is MSB, 0 is LSB

31