Slides for Lecture 21

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

27 March, 2014

ENCM 501 W14 Slides for Lecture 21

slide 2/22

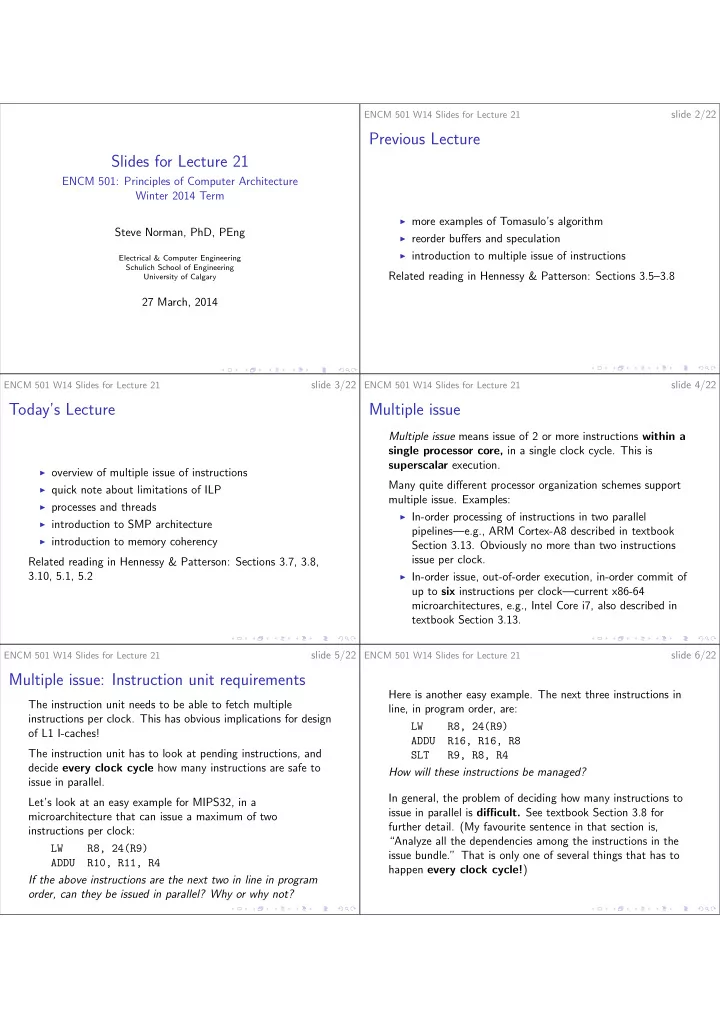

Previous Lecture

◮ more examples of Tomasulo’s algorithm ◮ reorder buffers and speculation ◮ introduction to multiple issue of instructions

Related reading in Hennessy & Patterson: Sections 3.5–3.8

ENCM 501 W14 Slides for Lecture 21

slide 3/22

Today’s Lecture

◮ overview of multiple issue of instructions ◮ quick note about limitations of ILP ◮ processes and threads ◮ introduction to SMP architecture ◮ introduction to memory coherency

Related reading in Hennessy & Patterson: Sections 3.7, 3.8, 3.10, 5.1, 5.2

ENCM 501 W14 Slides for Lecture 21

slide 4/22

Multiple issue

Multiple issue means issue of 2 or more instructions within a single processor core, in a single clock cycle. This is superscalar execution. Many quite different processor organization schemes support multiple issue. Examples:

◮ In-order processing of instructions in two parallel

pipelines—e.g., ARM Cortex-A8 described in textbook Section 3.13. Obviously no more than two instructions issue per clock.

◮ In-order issue, out-of-order execution, in-order commit of

up to six instructions per clock—current x86-64 microarchitectures, e.g., Intel Core i7, also described in textbook Section 3.13.

ENCM 501 W14 Slides for Lecture 21

slide 5/22

Multiple issue: Instruction unit requirements

The instruction unit needs to be able to fetch multiple instructions per clock. This has obvious implications for design

- f L1 I-caches!

The instruction unit has to look at pending instructions, and decide every clock cycle how many instructions are safe to issue in parallel. Let’s look at an easy example for MIPS32, in a microarchitecture that can issue a maximum of two instructions per clock: LW R8, 24(R9) ADDU R10, R11, R4 If the above instructions are the next two in line in program

- rder, can they be issued in parallel? Why or why not?