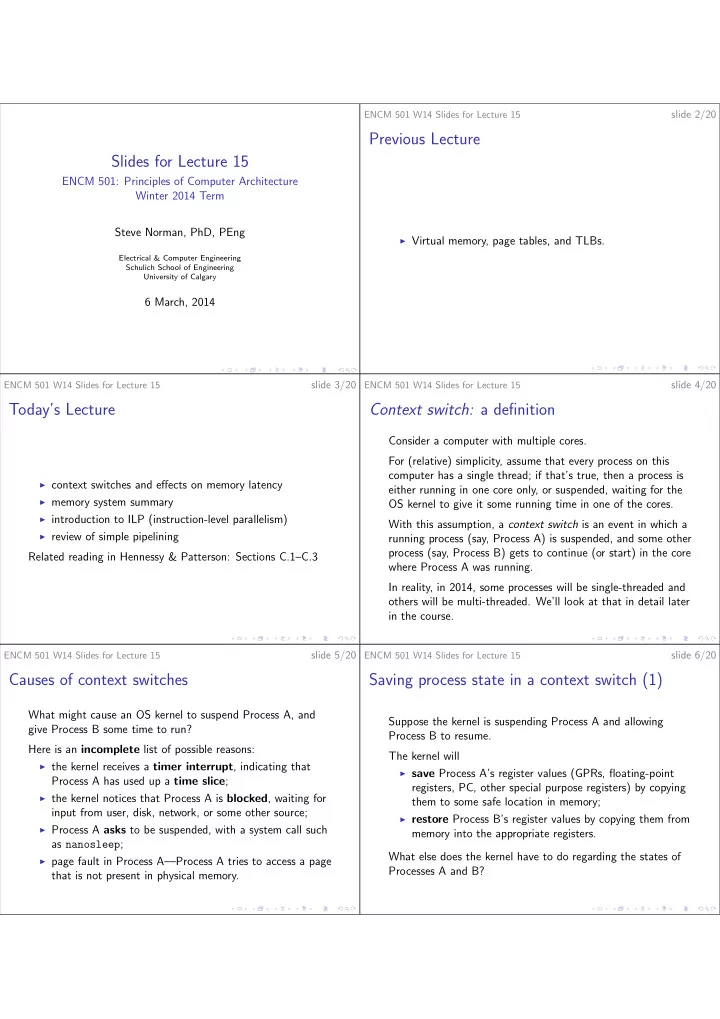

Slides for Lecture 15

ENCM 501: Principles of Computer Architecture Winter 2014 Term Steve Norman, PhD, PEng

Electrical & Computer Engineering Schulich School of Engineering University of Calgary

6 March, 2014

ENCM 501 W14 Slides for Lecture 15

slide 2/20

Previous Lecture

◮ Virtual memory, page tables, and TLBs.

ENCM 501 W14 Slides for Lecture 15

slide 3/20

Today’s Lecture

◮ context switches and effects on memory latency ◮ memory system summary ◮ introduction to ILP (instruction-level parallelism) ◮ review of simple pipelining

Related reading in Hennessy & Patterson: Sections C.1–C.3

ENCM 501 W14 Slides for Lecture 15

slide 4/20

Context switch: a definition

Consider a computer with multiple cores. For (relative) simplicity, assume that every process on this computer has a single thread; if that’s true, then a process is either running in one core only, or suspended, waiting for the OS kernel to give it some running time in one of the cores. With this assumption, a context switch is an event in which a running process (say, Process A) is suspended, and some other process (say, Process B) gets to continue (or start) in the core where Process A was running. In reality, in 2014, some processes will be single-threaded and

- thers will be multi-threaded. We’ll look at that in detail later

in the course.

ENCM 501 W14 Slides for Lecture 15

slide 5/20

Causes of context switches

What might cause an OS kernel to suspend Process A, and give Process B some time to run? Here is an incomplete list of possible reasons:

◮ the kernel receives a timer interrupt, indicating that

Process A has used up a time slice;

◮ the kernel notices that Process A is blocked, waiting for

input from user, disk, network, or some other source;

◮ Process A asks to be suspended, with a system call such

as nanosleep;

◮ page fault in Process A—Process A tries to access a page

that is not present in physical memory.

ENCM 501 W14 Slides for Lecture 15

slide 6/20

Saving process state in a context switch (1)

Suppose the kernel is suspending Process A and allowing Process B to resume. The kernel will

◮ save Process A’s register values (GPRs, floating-point

registers, PC, other special purpose registers) by copying them to some safe location in memory;

◮ restore Process B’s register values by copying them from