Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

IC Project and Verification

- Digital -

Introduction

Joachim Rodrigues, Assistant Professor Henrik Sjöland, Professor

Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

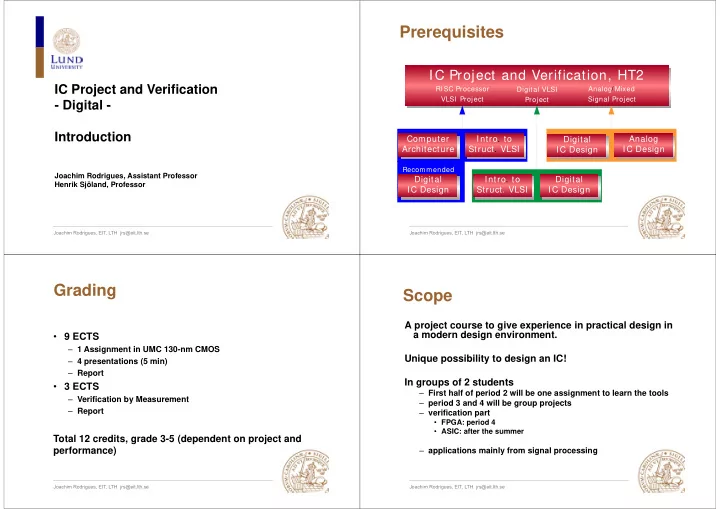

Prerequisites

IC Project and Verification, HT2

Digital VLSI Project

Digital IC Design Computer Architecture

- Intro. to

- Struct. VLSI

Analog IC Design

RISC Processor VLSI Project Analog/ Mixed Signal Project

Digital IC Design

- Intro. to

- Struct. VLSI

Digital IC Design

Recommended

Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Grading

- 9 ECTS

– 1 Assignment in UMC 130-nm CMOS – 4 presentations (5 min) – Report

- 3 ECTS

– Verification by Measurement – Report

Total 12 credits, grade 3-5 (dependent on project and performance)

Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Scope

A project course to give experience in practical design in a modern design environment. Unique possibility to design an IC! In groups of 2 students

– First half of period 2 will be one assignment to learn the tools – period 3 and 4 will be group projects – verification part

- FPGA: period 4

- ASIC: after the summer

– applications mainly from signal processing