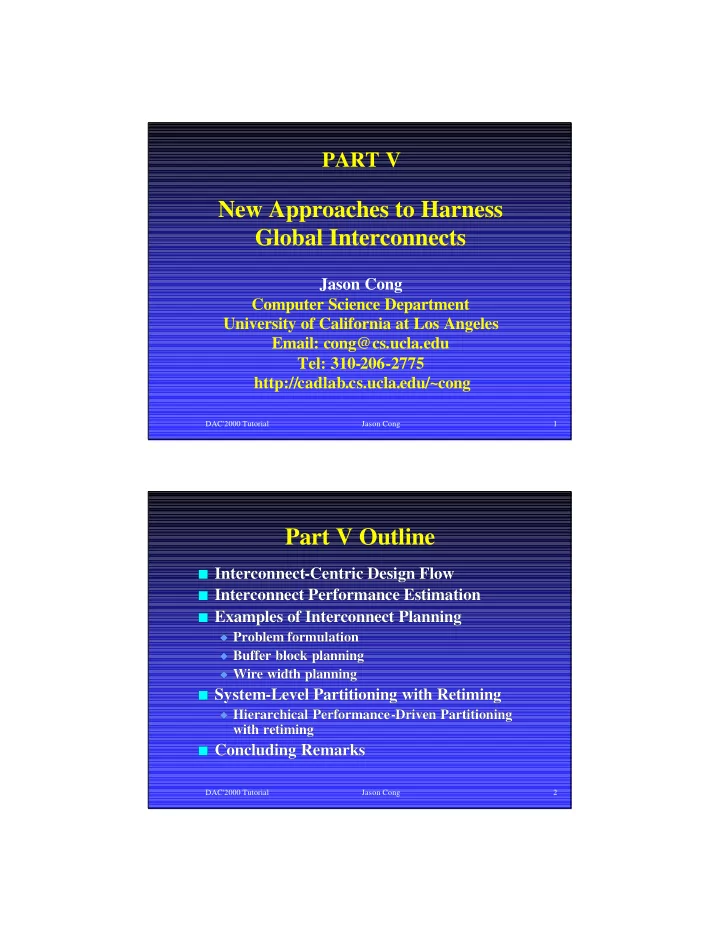

DAC'2000 Tutorial Jason Cong 1

PART V

New Approaches to Harness Global Interconnects

Jason Cong Computer Science Department University of California at Los Angeles Email: cong@cs.ucla.edu Tel: 310-206-2775 http://cadlab.cs.ucla.edu/~cong

DAC'2000 Tutorial Jason Cong 2

Part V Outline

I Interconnect

Interconnect-Centric Design Flow Centric Design Flow

I Interconnect Performance Estimation

Interconnect Performance Estimation

I Examples of Interconnect Planning

Examples of Interconnect Planning

N Problem formulation

Problem formulation

N Buffer block planning

Buffer block planning

N Wire width planning

Wire width planning

I System

System-Level Partitioning with Retiming Level Partitioning with Retiming

N Hierarchical Performance

Hierarchical Performance-Driven Partitioning Driven Partitioning with retiming with retiming

I Concluding Remarks