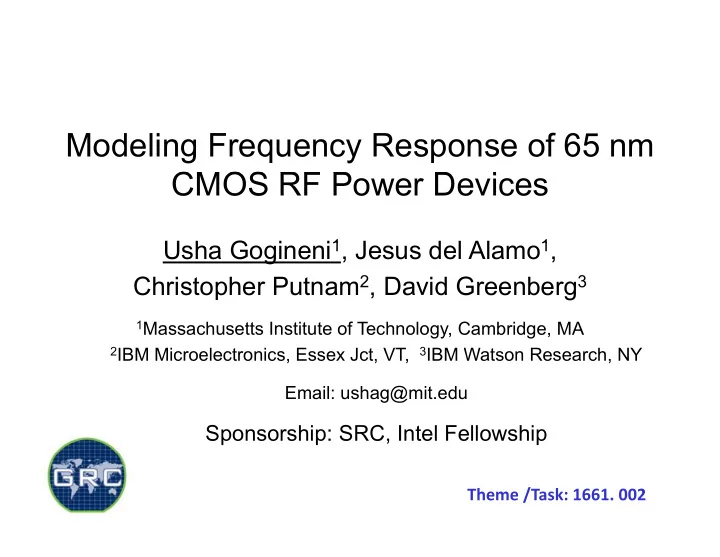

Modeling Frequency Response of 65 nm CMOS RF Power Devices CMOS RF - PowerPoint PPT Presentation

Modeling Frequency Response of 65 nm CMOS RF Power Devices CMOS RF P D i i 1 J Usha Gogineni 1 , Jesus del Alamo 1 , U h G i d l Al 1 Christopher Putnam 2 , David Greenberg 3 1 Massachusetts Institute of Technology, Cambridge, MA 2 IBM

Modeling Frequency Response of 65 nm CMOS RF Power Devices CMOS RF P D i i 1 J Usha Gogineni 1 , Jesus del Alamo 1 , U h G i d l Al 1 Christopher Putnam 2 , David Greenberg 3 1 Massachusetts Institute of Technology, Cambridge, MA 2 IBM Microelectronics, Essex Jct, VT, 3 IBM Watson Research, NY Email: ushag@mit.edu Sponsorship: SRC, Intel Fellowship Theme /Task: 1661. 002

Outline • Motivation • Measured Data on 65 nm CMOS – f T , f max as a function of device width • Small-signal Equivalent Circuit Extraction • Analytical Model for f and f • Analytical Model for f T and f max • Conclusions Conclusions Usha Gogineni / 1

Motivation • Great interest in using CMOS for mm-wave power applications • However, P out < 20 mW at 18 GHz [1] • Output power does not scale with width in wide devices 65nm CMOS 1. J. Scholvin, IEDM 2006 Usha Gogineni / 2

Motivation • Why doesn’t output power scale in wide devices? • High frequency power performance correlates with f max Key Questions: How does f max scale in wide devices? Can we predict f Can we predict f T , f max for a given device layout? f for a given device layout? Usha Gogineni / 3

Technology and Layout Details Gate Gate S D S D • 65 nm CMOS from IBM Sx Sx • Gate Length = 50 nm G t L th 50 Sx S • Gate Width = 96 m to 1536 m G Gate • Unit Cell: 24 fingers of 2 m width Unit cell: W = 48 m • W ↑ by parallelizing multiple unit cells Source • S-parameters from 0.5 GHz to 40 GHz • Open and short de-embedding p g Gate Gate Drain Drain Source 4 Unit cells: W = 192 m Usha Gogineni / 4

Measured Data - f T , f max f T ↓ and f max ↓ as W ↑ Usha Gogineni / 5

Small-signal Equivalent Circuit To understand f T , f max width scaling: construct small-signal equivalent circuit Usha Gogineni / 6

Small-signal Parameter Extraction Measure S-parameters Convert to Y-parameters 1. 3. g m @ @ V GS =V DS =0 V g Re( Y ( 21 ) ) GS DS m 21 Convert to Z-parameters 1 r o R G Re( Z Z ) Re( Y ) 11 12 22 R Re( Z ) Re( Y Y ) S 12 22 12 R sx 2 R Re( Z Z ) (Im( Y Y )) D 22 12 22 12 Im( ) Y Y Measure S-parameters @ 2. 11 12 C gs V DS =1 V, I D =100 mA/mm Im( Im( ) ) Y Y 12 12 Convert to Z-parameters C gd Subtract R G , R S , R D Im( Y Y ) 22 12 C C C C db db sb b Intrinsic Z-parameters C gb by fitting in ADS Ref: D. Lovelace, Microwave Symposium, 1994 Usha Gogineni / 7

Measured vs Modeled s-parameters W = 96 m V DD = 1 V I I D = 100 mA/mm 100 A/ Modeled Measured Model fits measured s-parameters well Usha Gogineni / 8

Measured vs Modeled f T , f max W = 96 m V DD = 1 V I = 100 mA/mm I D = 100 mA/mm Model fits measured h 21 and U at all frequencies Usha Gogineni / 9

Width Dependence of Intrinsic Parameters V DD = 1V V DD 1V I D = 100 mA/mm = 1/r o Intrinsic parameters scale ideally with W Usha Gogineni / 10

Width Dependence of Parasitic Resistances V DD = 1V I = 100 mA/mm I D = 100 mA/mm Source Gate Drain Source 2 cells 8 cells 32 cells R S constant, R G ↑ and R D ↑ as W ↑ Usha Gogineni / 11

f T , f max sensitivity f T , f max sensitivity to 100% change in small-signal parameters: ‐ 50 f max (%) ‐ 40 ‐ 30 n f T and f ‐ 20 ‐ 10 10 Change in 0 10 10 C 20 Scale ideally Scale ideally Minor Impact Minor Impact R G , R D have big impact on f max and do not scale well Usha Gogineni / 12

Reason for f max degradation Does poor scalability of R G , R D alone explain f max degradation? Use small-signal model for W = 96 m device in ADS Use small signal model for W 96 m device in ADS R G ↑ 120% and R D ↑ 180% keeping all else constant f T f max Modeled R ↑ 142 GHz → 112 GHz 180 GHz → 95 GHz W: 96 m. R G , R D ↑ W 96 R Measured W: 96 m -1536 m 142 GHz → 110 GHz 190 GHz → 90 GHz W: 96 m 1536 m W ↑ f T ↓ because R D ↑ W ↑ f max ↓ because R G and R D ↑ Usha Gogineni / 13

Analytical Expressions for f T , f max • Useful to have simple expressions for f T and f max • Substrate parameters (R sx , C db , C sb , C gb ) ignored • 2 and higher order terms ignored • Traditional derivations for f max only include R G Tasker’s [2] expression: g m f T R R R R 1 1 D S 2 C ( 1 ) C ( 1 ( R R )( g )) gs gd D S m r r o o New expression: g g 1 1 g g R R g g ( ( R R R R ) ) m m S ds D S f max 2 2 4 [ C ( R R ) g ( 1 g R ) C (( R R )( g g ) gs G S ds m S gd G D m ds 2 ( g g ) ( 2 R R R R 2 R R )) C C ( R ( g 2 g ) m ds G S G D S D gs gd G m ds 2 g g ( 5 R R 3 R R 2 R R ) g R R )] m ds G S G D S D m G S 2. Tasker, EDL ‘89 Usha Gogineni / 14

Measured and Analytical f T , f max • Excellent agreement between analytical and measured data g y • Model useful to understand impact of width scaling on high frequency characteristics Usha Gogineni / 15

Conclusions • Studied frequency response of 65 nm CMOS devices • f T and f max decrease with increasing device width • Accurate small signal circuit parameters extracted • Accurate small-signal circuit parameters extracted • f T , f max ↓ because R G and R D ↑ as W ↑ • Analytical model of f T , f max models width behavior well Key to enabling CMOS for mm-wave applications is a parasitic-aware approach when designing wide devices iti h h d i i id d i Usha Gogineni / 16

Technology Transfer Liaison Interactions: • Industrial Liaisons: David Greenberg, Alberto Valdes Garcia (IBM Microelectronics) (IBM Microelectronics) • Several teleconferences with liaisons over academic year • More frequent interaction during internships q g p • Device designs done with input from Liaisons Internships: • Summer 2007 and summer 2008 at IBM Microelectronics • Design work carried out at IBM Microelectronics • 65 nm and 45 nm designs manufactured by IBM • 65 nm and 45 nm designs manufactured by IBM Publications / Presentations: Task reports published on SRC website regularly Task reports published on SRC website regularly SiRF 2010: 45 nm power and frequency response Usha Gogineni / 17

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.