1

CMOS Inverter

Professor Chris H. Kim

University of Minnesota

- Dept. of ECE

chriskim@umn.edu www.umn.edu/~chriskim/

2

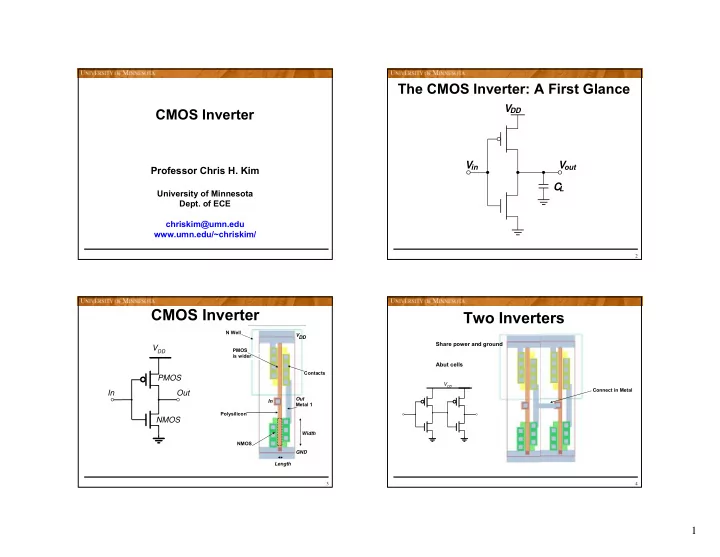

The CMOS Inverter: A First Glance

Vin Vout C

L

V

DD

3

CMOS Inverter

Polysilicon In Out VDD GND PMOS is wider Metal 1 NMOS

Out In VDD PMOS NMOS

Contacts N Well Length Width 4

Two Inverters

Connect in Metal

Share power and ground Abut cells

VDD