SLIDE 1

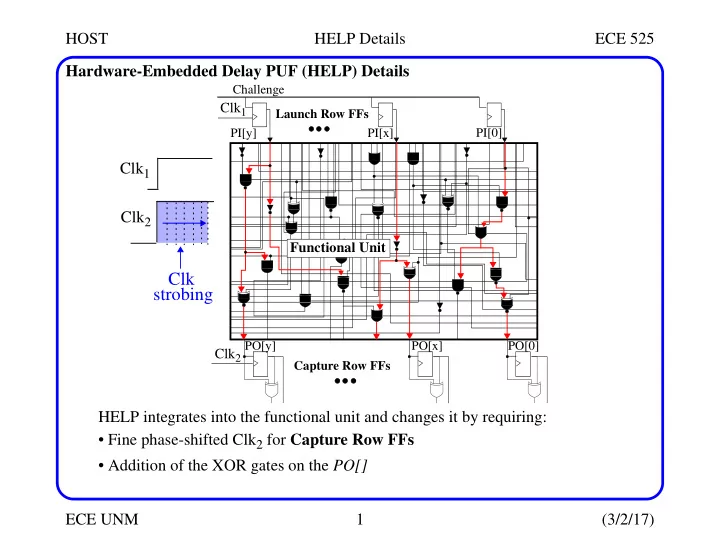

HOST HELP Details ECE 525 ECE UNM 1 (3/2/17) Hardware-Embedded Delay PUF (HELP) Details HELP integrates into the functional unit and changes it by requiring:

- Fine phase-shifted Clk2 for Capture Row FFs

- Addition of the XOR gates on the PO[]