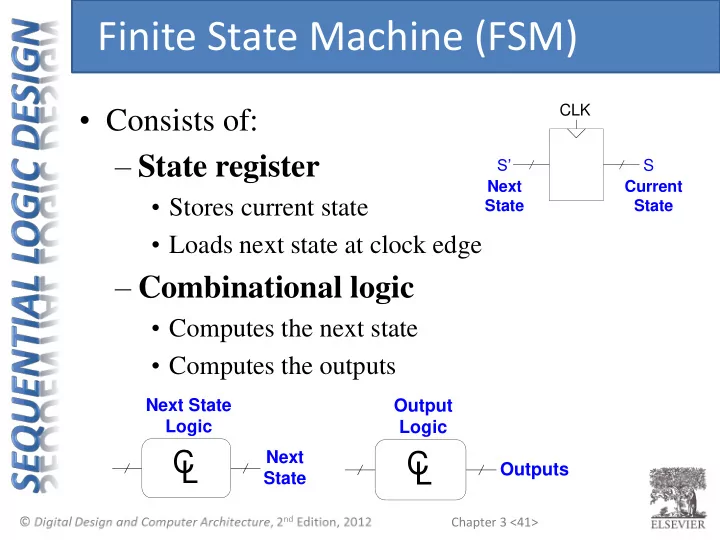

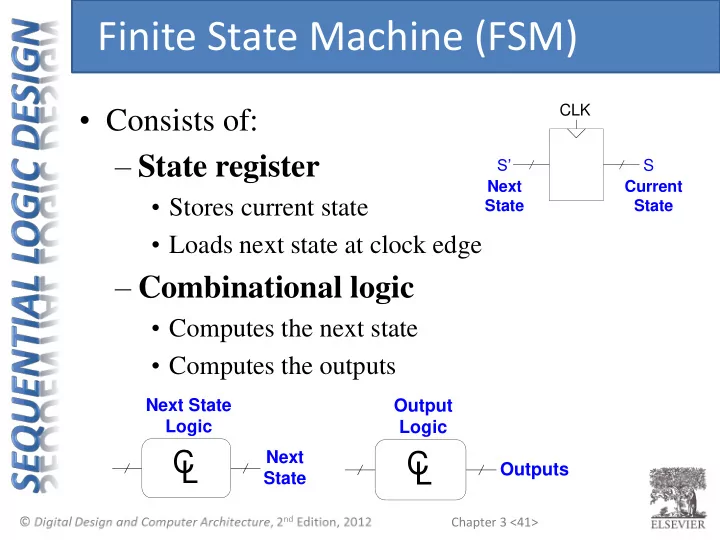

Finite State Machine (FSM) • Consists of: CLK – State register S’ S Next Current • Stores current state State State • Loads next state at clock edge – Combinational logic • Computes the next state • Computes the outputs Next State Output Logic Logic C Next C L L Outputs State Chapter 3 <41>

Finite State Machines (FSMs) • Next state determined by current state and inputs • Two types of finite state machines differ in output logic: – Moore FSM: outputs depend only on current state – Mealy FSM: outputs depend on current state and inputs Moore FSM CLK next M k k N next state output inputs state outputs state logic logic Mealy FSM CLK M next k k N next output inputs state state outputs state logic logic Chapter 3 <42>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <43>

FSM Example • Traffic light controller – Traffic sensors: T A , T B (TRUE when there’s traffic) – Lights: L A , L B Bravado Dining Hall L B L A T B L A Academic Ave. T A T A Dorms L B T B Labs Blvd. Fields Chapter 3 <44>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <45>

FSM Black Box • Inputs: CLK , Reset , T A , T B • Outputs: L A , L B CLK Note: multiple bits for output Traffic T A L A Light T B L B Controller Reset Chapter 3 <46>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <47>

FSM State Transition Diagram • Moore FSM: outputs labeled in each state • States: Circles Reset • Transitions: Arcs S0 L A : green L B : red Bravado Dining Hall L B L A T B L A Academic Ave. T A T A Dorms L B T B Labs Blvd. Fields Chapter 3 <48>

FSM State Transition Diagram • Moore FSM: outputs labeled in each state • States: Circles T A Reset • Transitions: Arcs T A S0 S1 L A : green L A : yellow L B : red L B : red Bravado Dining Hall L B L A T B L A Academic Ave. T A T A S3 S2 Dorms L A : red L A : red L B T B Labs L B : yellow L B : green T B Blvd. Fields T B Chapter 3 <49>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <50>

FSM State Transition Table T A Reset T A S0 S1 L A : green L A : yellow L B : red L B : red Current Next State Inputs State S3 S2 L A : red L A : red L B : yellow L B : green T B T B S T A T B S' S0 0 X S0 1 X S1 X X S2 X 0 S2 X 1 S3 X X Chapter 3 <51>

FSM State Transition Table T A Reset T A S0 S1 L A : green L A : yellow L B : red L B : red Current Next State Inputs State S3 S2 L A : red L A : red L B : yellow L B : green T B T B S T A T B S' S0 0 X S1 S0 1 X S0 S1 X X S2 S2 X 0 S3 S2 X 1 S2 S3 X X S0 Chapter 3 <52>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <53>

FSM Encoded State Transition Table Current State Inputs Next State S 1 S 0 T A T B S' 1 S' 0 State Encoding 0 0 0 X S0 00 0 0 1 X S1 01 0 1 X X 1 0 X 0 S2 10 1 0 X 1 S3 11 1 1 X X Two bits required for 4 states T A Reset T A S0 S1 L A : green L A : yellow L B : red L B : red S3 S2 L A : red L A : red L B : yellow L B : green T B T B Chapter 3 <54>

FSM Encoded State Transition Table Current State Inputs Next State S 1 S 0 T A T B S' 1 S' 0 State Encoding 0 0 0 X 0 1 S0 00 0 0 1 X 0 0 S1 01 0 1 X X 1 0 1 0 X 0 1 1 S2 10 1 0 X 1 1 0 S3 11 1 1 X X 0 0 Two bits required for 4 states T A S' 1 = S 1 S 0 Reset T A S0 S1 L A : green L A : yellow L B : red L B : red S' 0 = S 1 S 0 T A + S 1 S 0 T B S3 S2 L A : red L A : red L B : yellow L B : green T B T B Chapter 3 <55>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <56>

FSM Output Table Current State Outputs Output Encoding S 1 S 0 L A 1 L A 0 L B 1 L B 0 green 00 0 0 0 1 yellow 01 1 0 red 10 1 1 Two bits required for 3 outputs T A Reset T A S0 S1 L A : green L A : yellow L B : red L B : red S3 S2 L A : red L A : red L B : yellow L B : green T B T B Chapter 3 <57>

FSM Output Table Current State Outputs Output Encoding S 1 S 0 L A 1 L A 0 L B 1 L B 0 green 00 0 0 0 0 1 0 0 1 0 1 1 0 yellow 01 1 0 1 0 0 0 red 10 1 1 1 0 0 1 Two bits required for 3 outputs L A 1 = S 1 L A 0 = S 1 S 0 T A Reset T A L B 1 = S 1 S0 S1 L A : green L A : yellow L B : red L B : red L B 0 = S 1 S 0 S3 S2 L A : red L A : red L B : yellow L B : green T B T B Chapter 3 <58>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <59>

FSM Schematic: State Register CLK S' 1 S 1 S' 0 S 0 r Reset state register S' 1 = S 1 S 0 L A 1 = S 1 L B 1 = S 1 S' 0 = S 1 S 0 T A + S 1 S 0 T B L A 0 = S 1 S 0 L B 0 = S 1 S 0 Chapter 3 <60>

FSM Schematic: Next State Logic CLK S' 1 S 1 T A S' 0 S 0 r T B Reset S 1 S 0 inputs next state logic state register S' 1 = S 1 S 0 S' 0 = S 1 S 0 T A + S 1 S 0 T B Chapter 3 <61>

FSM Schematic: Output Logic CLK L A1 S' 1 S 1 L A0 T A S' 0 S 0 L B1 r T B Reset S 1 S 0 L B0 inputs next state logic state register output logic outputs L A 1 = S 1 L B 1 = S 1 L A 0 = S 1 S 0 L B 0 = S 1 S 0 Chapter 3 <62>

FSM Timing Diagram Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7 Cycle 8 Cycle 9 Cycle 10 CLK Reset T A T B S' 1:0 ?? S0 (00) S1 (01) S2 (10) S3 (11) S0 (00) S1 (01) S 1:0 ?? S0 (00) S1 (01) S2 (10) S3 (11) S0 (00) L A1:0 ?? Green (00) Yellow (01) Red (10) Green (00) L B1:0 ?? Red (10) Green (00) Yellow (01) Red (10) t (sec) 0 5 10 15 20 25 30 35 40 45 T A Reset T A S0 S1 L A : green L A : yellow L B : red L B : red S3 S2 L A : red L A : red L B : yellow L B : green T B T B Chapter 3 <63>

FSM State Encoding • Binary encoding: – i.e., for four states, 00, 01, 10, 11 • One-hot encoding – One state bit per state – Only one state bit HIGH at once – i.e., for 4 states, 0001, 0010, 0100, 1000 – Requires more flip-flops – Often next state and output logic is simpler Chapter 3 <64>

FSM Design Procedure 1. Identify inputs and outputs 2. Sketch state transition diagram 3. Write state transition table 4. Select state encodings 5. Rewrite state transition table with state encodings 6. Write output table 7. Write Boolean equations for next state and output logic 8. Sketch the circuit schematic Chapter 3 <65>

Recommend

More recommend