VHDL - Flaxer Eli Ch 4 - 1

Object & Type

Chapter 4 Data Object and Type

VHDL

VHDL - Flaxer Eli Ch 4 - 2

Object & Type

Outline

Keyword Identifiers & Comment Data Object Data Type Scalar Type Composite Type Pointer Type Incomplete Types File Type

VHDL - Flaxer Eli Ch 4 - 3

Object & Type

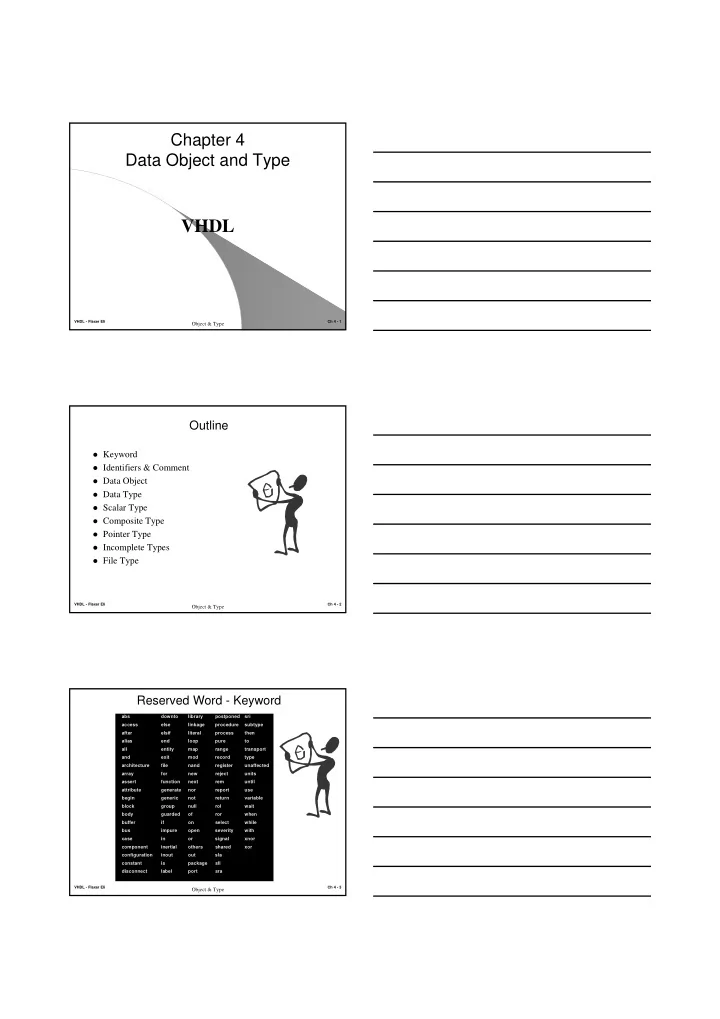

Reserved Word - Keyword

abs downto library postponed sri access else linkage procedure subtype after elsif literal process then alias end loop pure to all entity map range transport and exit mod record type architecture file nand register unaffected array for new reject units assert function next rem until attribute generate nor report use begin generic not return variable block group null rol wait body guarded

- f

ror when buffer if

- n

select while bus impure

- pen

severity with case in

- r

signal xnor component inertial

- thers

shared xor configuration inout

- ut

sla constant is package sll disconnect label port sra