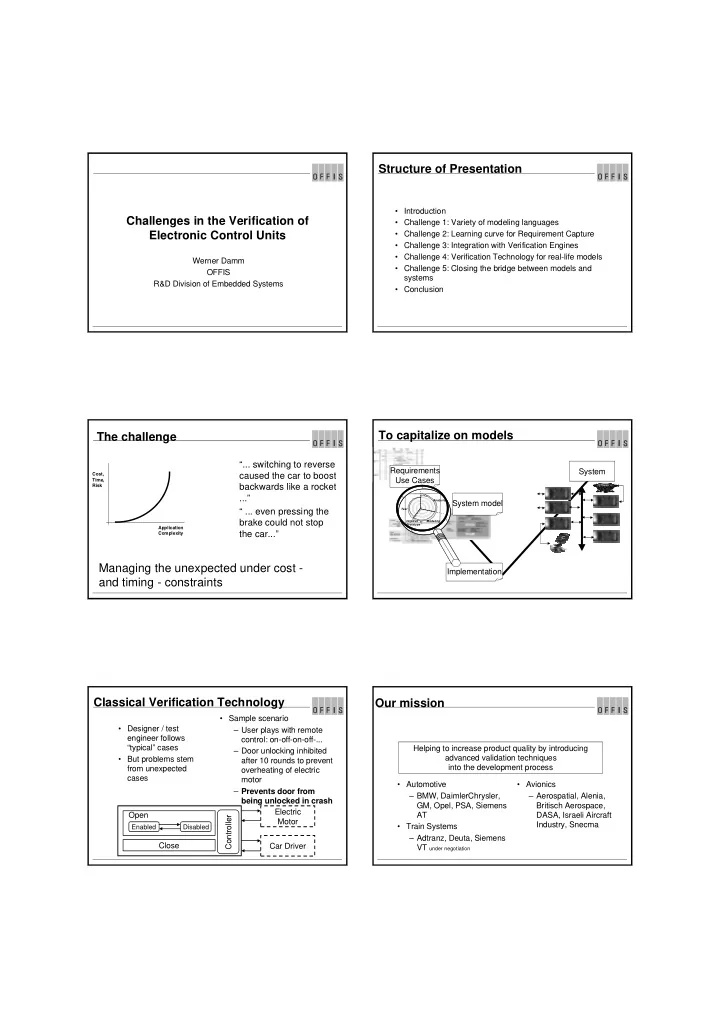

Challenges in the Verification of Electronic Control Units

Werner Damm OFFIS R&D Division of Embedded Systems

Structure of Presentation

- Introduction

- Challenge 1: Variety of modeling languages

- Challenge 2: Learning curve for Requirement Capture

- Challenge 3: Integration with Verification Engines

- Challenge 4: Verification Technology for real-life models

- Challenge 5: Closing the bridge between models and

systems

- Conclusion

The challenge

“... switching to reverse caused the car to boost backwards like a rocket ...” “ ... even pressing the brake could not stop the car...”

Cost, Time, Risk Application ComplexityManaging the unexpected under cost - and timing - constraints To capitalize on models

System System model Requirements Use Cases Implementation

Analysis Modeling Test Iterative Prototype *Classical Verification Technology

- Designer / test

engineer follows “typical” cases

- But problems stem

from unexpected cases

- Sample scenario

– User plays with remote control: on-off-on-off-... – Door unlocking inhibited after 10 rounds to prevent

- verheating of electric

motor – Prevents door from being unlocked in crash Electric Motor Car Driver Close

Enabled Disabled

Open Controller

Our mission

- Automotive

– BMW, DaimlerChrysler, GM, Opel, PSA, Siemens AT

- Train Systems

– Adtranz, Deuta, Siemens VT under negotiation

- Avionics

– Aerospatial, Alenia, Britisch Aerospace, DASA, Israeli Aircraft Industry, Snecma Helping to increase product quality by introducing advanced validation techniques into the development process