Page 1

Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

KU Leuven - COSIC Digital CMOS - 1 Albena, July 2013

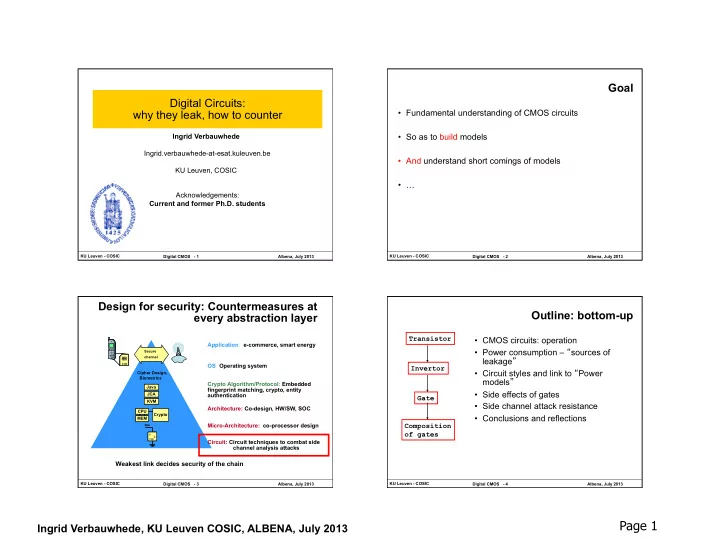

Digital Circuits: why they leak, how to counter

Ingrid Verbauwhede Ingrid.verbauwhede-at-esat.kuleuven.be KU Leuven, COSIC Acknowledgements: Current and former Ph.D. students

KU Leuven - COSIC Digital CMOS - 2 Albena, July 2013

Goal

- Fundamental understanding of CMOS circuits

- So as to build models

- And understand short comings of models

- …

KU Leuven - COSIC Digital CMOS - 3 Albena, July 2013

Design for security: Countermeasures at every abstraction layer

Cipher Design, Biometrics

D Q Vcc

CPU Crypto MEM JCA Java JVM

CLK

Secure channel

SIM D Q Vcc

CPU MEM JCA Java KVM

CLK

OS: Operating system Crypto Algorithm/Protocol: Embedded fingerprint matching, crypto, entity authentication Architecture: Co-design, HW/SW, SOC Circuit: Circuit techniques to combat side channel analysis attacks Micro-Architecture: co-processor design

SIM SIM SIM

Weakest link decides security of the chain

Application: e-commerce, smart energy

KU Leuven - COSIC Digital CMOS - 4 Albena, July 2013

Outline: bottom-up

- CMOS circuits: operation

- Power consumption – “sources of

leakage”

- Circuit styles and link to “Power

models”

- Side effects of gates

- Side channel attack resistance

- Conclusions and reflections

Transistor Invertor Gate Composition

- f gates