Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Introduction to Structured VLSI Design ‐ VHDL V

Joachim Rodrigues

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

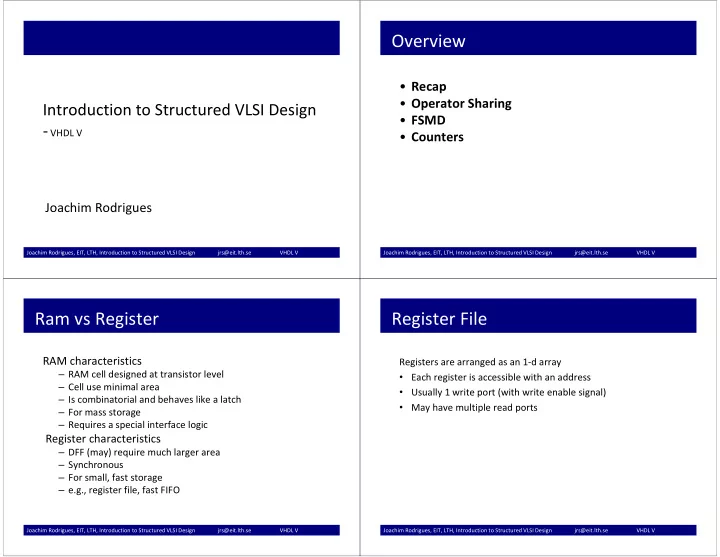

Overview

- Recap

- Operator Sharing

- FSMD

- Counters

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Ram vs Register

RAM characteristics

– RAM cell designed at transistor level – Cell use minimal area – Is combinatorial and behaves like a latch – For mass storage – Requires a special interface logic

Register characteristics

– DFF (may) require much larger area – Synchronous – For small, fast storage – e.g., register file, fast FIFO

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Register File

Registers are arranged as an 1‐d array

- Each register is accessible with an address

- Usually 1 write port (with write enable signal)

- May have multiple read ports