SLIDE 1

1 IC220 Set #19: Laundry, Co-dependency, and other Hazards

- f Modern (Architecture) Life

Midnight Laundry 2 Smarty Laundry 3 Pipelining Improve - - PDF document

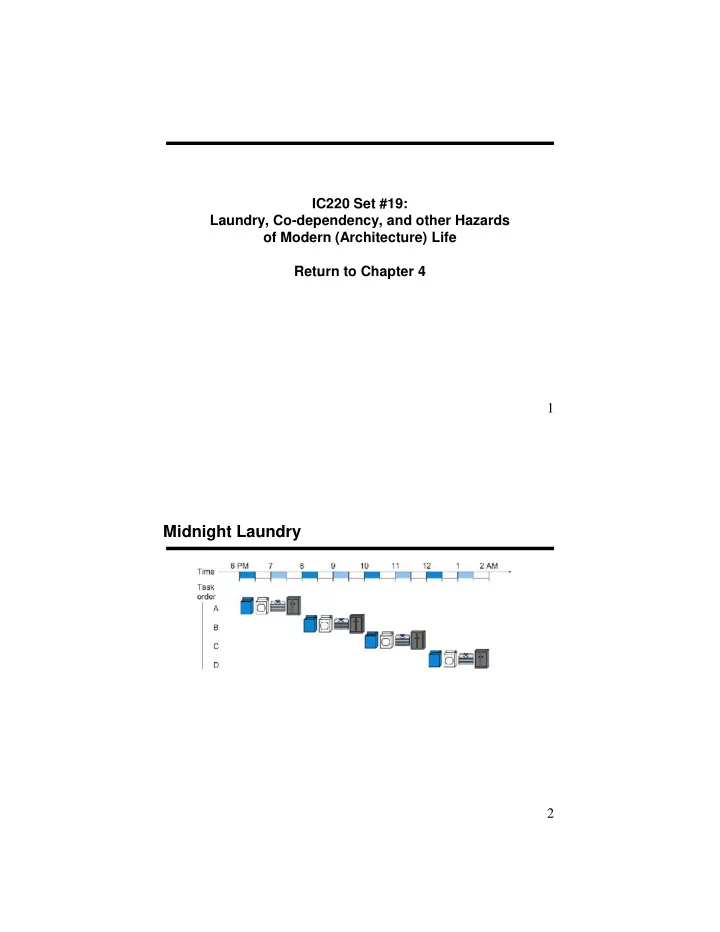

IC220 Set #19: Laundry, Co-dependency, and other Hazards of Modern (Architecture) Life Return to Chapter 4 1 Midnight Laundry 2 Smarty Laundry 3 Pipelining Improve performance by increasing instruction throughput Ideal speedup is

sub $s0, $s1, $s2 and $a1, $s0, $a3 add $t0, $t1, $s0

sub $s0, $s1, $s2 and $a1, $s0, $a3 add $t0, $t1, $s0

Execution/Address Calculation stage control lines Memory access stage control lines Write-back stage control lines Instruction Reg Dst ALU Op1 ALU Op0 ALU Src Branch Mem Read Mem Write Reg write Mem to Reg R-format 1 1 1 lw 1 1 1 1 sw X 1 1 X beq X 1 1 X