1 IC220 Set #19: Laundry, Co-dependency, and other Hazards

- f Modern (Architecture) Life

Return to Chapter 4 2

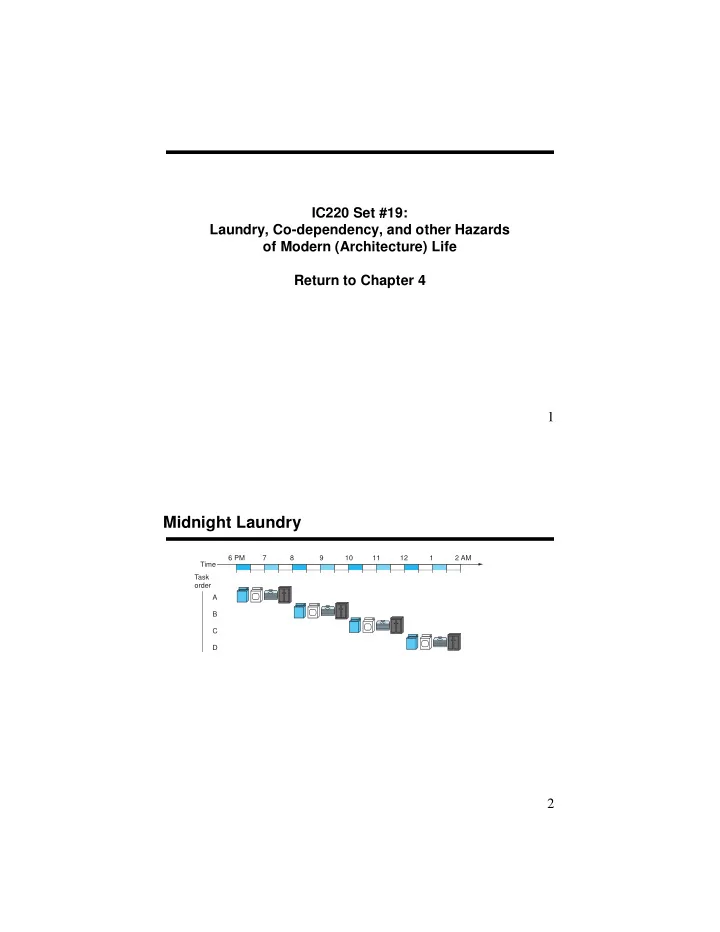

Midnight Laundry

Time 6 PM 7 8 9 10 11 12 1 2 AM Task

- rder

A

- B

- C

- D

Midnight Laundry 6 PM 7 8 9 - - PDF document

IC220 Set #19: Laundry, Co-dependency, and other Hazards of Modern (Architecture) Life Return to Chapter 4 1 Midnight Laundry 6 PM 7 8 9 10 11 12 1 2 AM Time

Time 6 PM 7 8 9 10 11 12 1 2 AM Task

A

Time 6 PM 7 8 9 10 11 12 1 2 AM Task

A

Time 6 PM 7 8 9 10 11 12 1 2 AM Task

A

Program execution

(in instructions) lw $1, 100($0) lw $2, 200($0) lw $3, 300($0) Time 200 400 600 800 1000 1200 1400 1600 1800 Instruction fetch R e g A L U Data a c ce ss R e g Instruction fetch R e g A L U Data a cc e ss R e g Instruction fetch 800 ps 800 ps 800 ps Program execution

(in instructions) lw $1, 100($0) lw $2, 200($0) lw $3, 300($0) Time 200 400 600 800 1000 1200 1400 Instruction fetch R e g A L U Data a cc e ss R e g Instruction fetch Instruction fetch R e g A L U Data a cc e ss R e g R e g A L U Data a c ce ss R e g 200 ps 200 ps 200 ps 200 ps 200 ps 200 ps 200 ps

WB: Write back MEM: Memory access IF: Instruction fetch ID: Instruction decode/ register file read EX: Execute/ address calculation

M u x

u x 1

Address

data Read data Data Memory Read register 1 Read register 2 Write register Write data Registers Read data 1 Read data 2 ALU Zero ALU result ADD

result Shift left 2 Address Instruction Instruction memory Add 4 PC Sign extend

M u x 1

16 32

Add Address Instruction memory Read register 1 Instruction Read register 2 Write register Write data Read data 1 Read data 2 Registers Address Write data Read data Data memory

Add Add result ALU ALU result Zero Shift left 2 Sign extend PC 4 ID/EX IF/ID EX/MEM MEM/WB 16 32

u x 1

u x 1

u x 1

Predict taken Predict taken Predict not taken Predict not taken Not taken Not taken Not taken Not taken Taken Taken Taken Taken

Add Address Instruction memory Read register 1 Instruction Read register 2 Write register Write data Read data 1 Read data 2 Registers Address Write data Read data Data memory

Add Add result ALU ALU result Zero Shift left 2 Sign extend PC 4 ID/EX IF/ID EX/MEM MEM/WB 16 32

u x 1

u x 1

u x 1

Execution/Address Calculation stage control lines Memory access stage control lines Write-back stage control lines Instruction Reg Dst ALU Op1 ALU Op0 ALU Src Branch Mem Read Mem Write Reg write Mem to Reg R-format 1 1 1 lw 1 1 1 1 sw X 1 1 X beq X 1 1 X

Control EX M WB M WB WB IF/ID ID/EX EX/MEM MEM/WB Instruction