2 02340 02340 Lectu cture 3 e 3 / / Ackn Acknow

- wledgemen

ledgement: Slides Slides from MI from MIT T cou course 6.004 6.004 prov

- vided by Prof.

ided by Prof. Wa Ward Sep rd Septemb ember 2004 r 2004

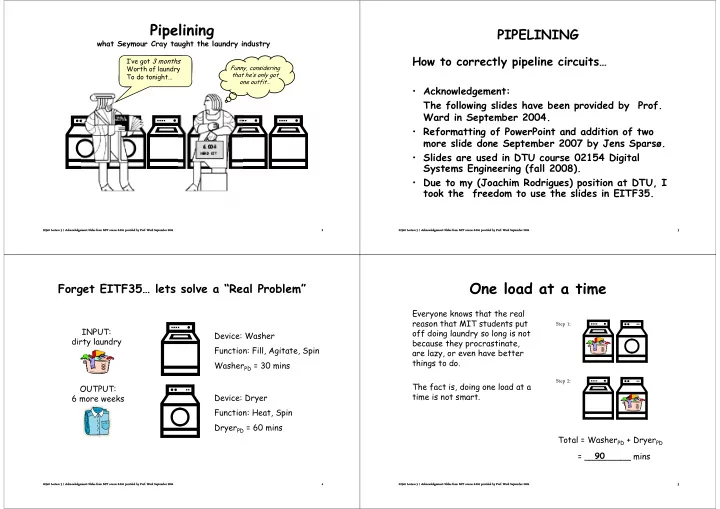

Pipelining

what Seymour Cray taught the laundry industry

I’ve got 3 months Worth of laundry To do tonight…

Funny, considering that he’s only got

- ne outfit…

3 02340 02340 Lectu cture 3 e 3 / / Ackn Acknow

- wledgemen

ledgement: Slides Slides from MI from MIT T cou course 6.004 6.004 prov

- vided by Prof.

ided by Prof. Wa Ward Sep rd Septemb ember 2004 r 2004

PIPELINING

How to correctly pipeline circuits…

- Acknowledgement:

The following slides have been provided by Prof. Ward in September 2004.

- Reformatting of PowerPoint and addition of two

more slide done September 2007 by Jens Sparsø.

- Slides are used in DTU course 02154 Digital

Systems Engineering (fall 2008).

- Due to my (Joachim Rodrigues) position at DTU, I

took the freedom to use the slides in EITF35.

4 02340 02340 Lectu cture 3 e 3 / / Ackn Acknow

- wledgemen

ledgement: Slides Slides from MI from MIT T cou course 6.004 6.004 prov

- vided by Prof.

ided by Prof. Wa Ward Sep rd Septemb ember 2004 r 2004

Forget EITF35… lets solve a “Real Problem”

Device: Washer Function: Fill, Agitate, Spin WasherPD = 30 mins Device: Dryer Function: Heat, Spin DryerPD = 60 mins INPUT: dirty laundry OUTPUT: 6 more weeks

5 02340 02340 Lectu cture 3 e 3 / / Ackn Acknow

- wledgemen

ledgement: Slides Slides from MI from MIT T cou course 6.004 6.004 prov

- vided by Prof.

ided by Prof. Wa Ward Sep rd Septemb ember 2004 r 2004

One load at a time

Everyone knows that the real reason that MIT students put

- ff doing laundry so long is not

because they procrastinate, are lazy, or even have better things to do. The fact is, doing one load at a time is not smart.

Step 1: Step 2:

Total = WasherPD + DryerPD = _________ mins 90