Introduction to Verilog Friday, January 05, 2001 9:34 pm Peter M. Nyasulu

9

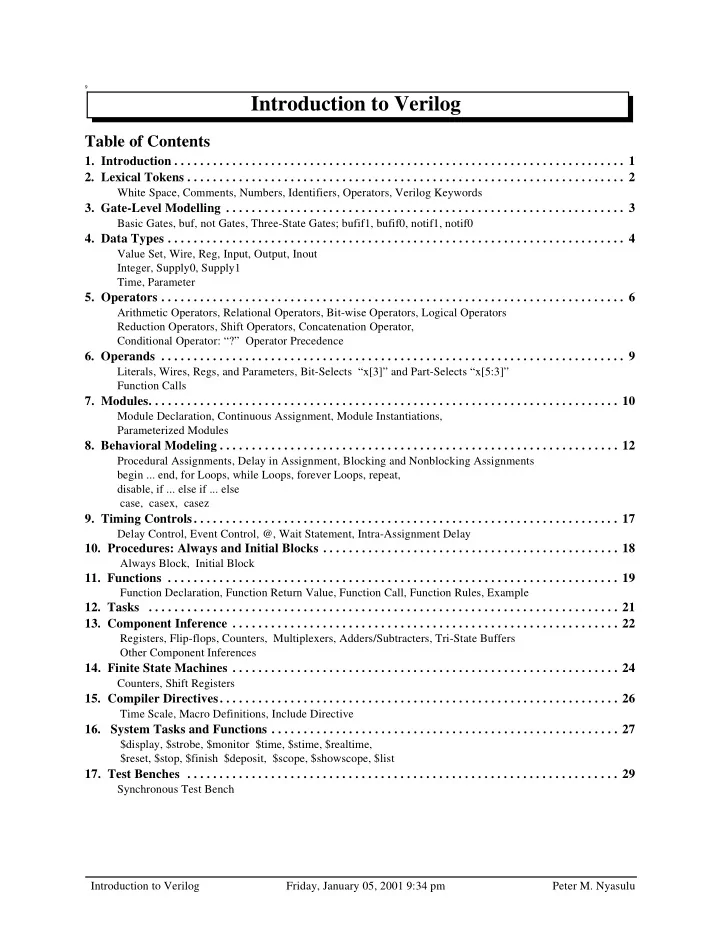

Table of Contents

- 1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

- 2. Lexical Tokens . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

White Space, Comments, Numbers, Identifiers, Operators, Verilog Keywords

- 3. Gate-Level Modelling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Basic Gates, buf, not Gates, Three-State Gates; bufif1, bufif0, notif1, notif0

- 4. Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Value Set, Wire, Reg, Input, Output, Inout Integer, Supply0, Supply1 Time, Parameter

- 5. Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Arithmetic Operators, Relational Operators, Bit-wise Operators, Logical Operators Reduction Operators, Shift Operators, Concatenation Operator, Conditional Operator: “?” Operator Precedence

- 6. Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Literals, Wires, Regs, and Parameters, Bit-Selects “x[3]” and Part-Selects “x[5:3]” Function Calls

- 7. Modules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Module Declaration, Continuous Assignment, Module Instantiations, Parameterized Modules

- 8. Behavioral Modeling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Procedural Assignments, Delay in Assignment, Blocking and Nonblocking Assignments begin ... end, for Loops, while Loops, forever Loops, repeat, disable, if ... else if ... else case, casex, casez

- 9. Timing Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Delay Control, Event Control, @, Wait Statement, Intra-Assignment Delay

- 10. Procedures: Always and Initial Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Always Block, Initial Block

- 11. Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Function Declaration, Function Return Value, Function Call, Function Rules, Example

- 12. Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

- 13. Component Inference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Registers, Flip-flops, Counters, Multiplexers, Adders/Subtracters, Tri-State Buffers Other Component Inferences

- 14. Finite State Machines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Counters, Shift Registers

- 15. Compiler Directives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Time Scale, Macro Definitions, Include Directive

- 16. System Tasks and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

$display, $strobe, $monitor $time, $stime, $realtime, $reset, $stop, $finish $deposit, $scope, $showscope, $list

- 17. Test Benches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29