1

CALTECH CS137 Fall2005 -- DeHon 1

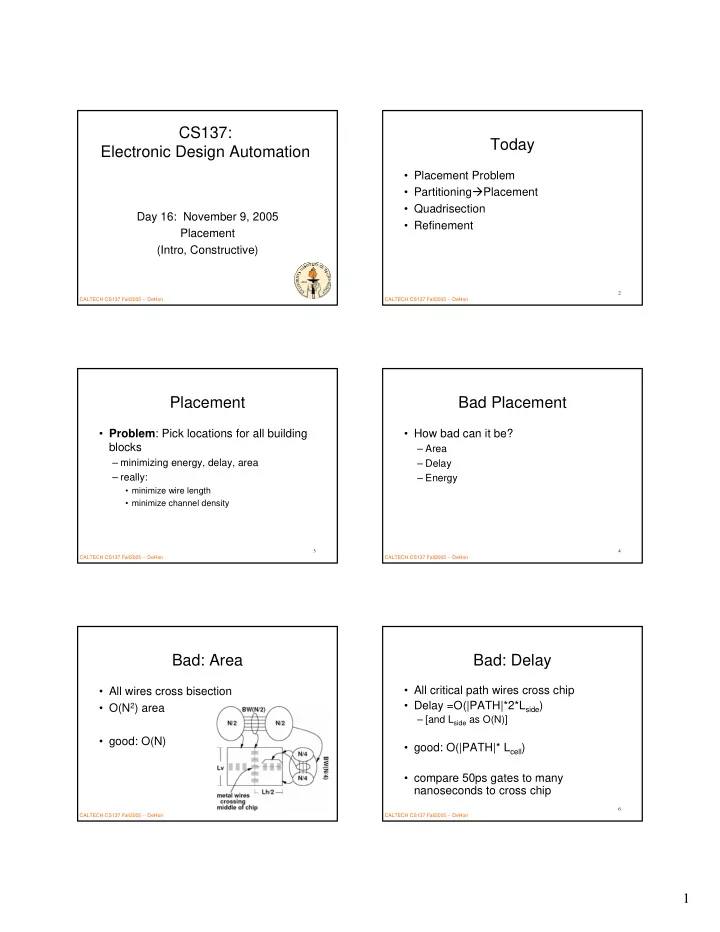

CS137: Electronic Design Automation

Day 16: November 9, 2005 Placement (Intro, Constructive)

CALTECH CS137 Fall2005 -- DeHon 2

Today

- Placement Problem

- PartitioningPlacement

- Quadrisection

- Refinement

CALTECH CS137 Fall2005 -- DeHon 3

Placement

- Problem: Pick locations for all building

blocks

– minimizing energy, delay, area – really:

- minimize wire length

- minimize channel density

CALTECH CS137 Fall2005 -- DeHon 4

Bad Placement

- How bad can it be?

– Area – Delay – Energy

CALTECH CS137 Fall2005 -- DeHon 5

Bad: Area

- All wires cross bisection

- O(N2) area

- good: O(N)

CALTECH CS137 Fall2005 -- DeHon 6

Bad: Delay

- All critical path wires cross chip

- Delay =O(|PATH|*2*Lside)

– [and Lside as O(N)]

- good: O(|PATH|* Lcell)

- compare 50ps gates to many