SLIDE 4 4

Graph Notation of Circuit

w(euv) = #latencies between u and v

u v

w(euv) = 2

u v

delay = d(u) delay = d(v)

r(u) is # latencies moved across gate u r(PI) = r(PO) = 0: Merge them both into a “host” node h with r(h) = 0 wr(euv) = w(euv) + r(v) - r(u)

r(u) = 1 w(euv) = 1

u v

r(v) = 2

u v

wr(euv) = 2

For a path from v1 to vk

- Consider a path of vertices

D fi ( t ) + + +

v1 v2 v3 vk w12 w23 w34 Wk-1,k

– Define w(v1 to vk) = w12 + w23 + … + w(k-1,k) – After retiming, wr(v1 to vk) = w12r + w23r + … + w(k-1,k)r

= [w12+r(2)–r(1)]+[w23+r(3)–r(2)]+[w23+r(3)–r(2)]+…+[w(k-1,k)+r(k)–r(k-1)] = w(v1 to vk) + r(k) – r(1) – For a cycle, v1 = vk, which implies that wr = w for a cycle – In other words, retiming leaves the # latencies unchanged on any cycle

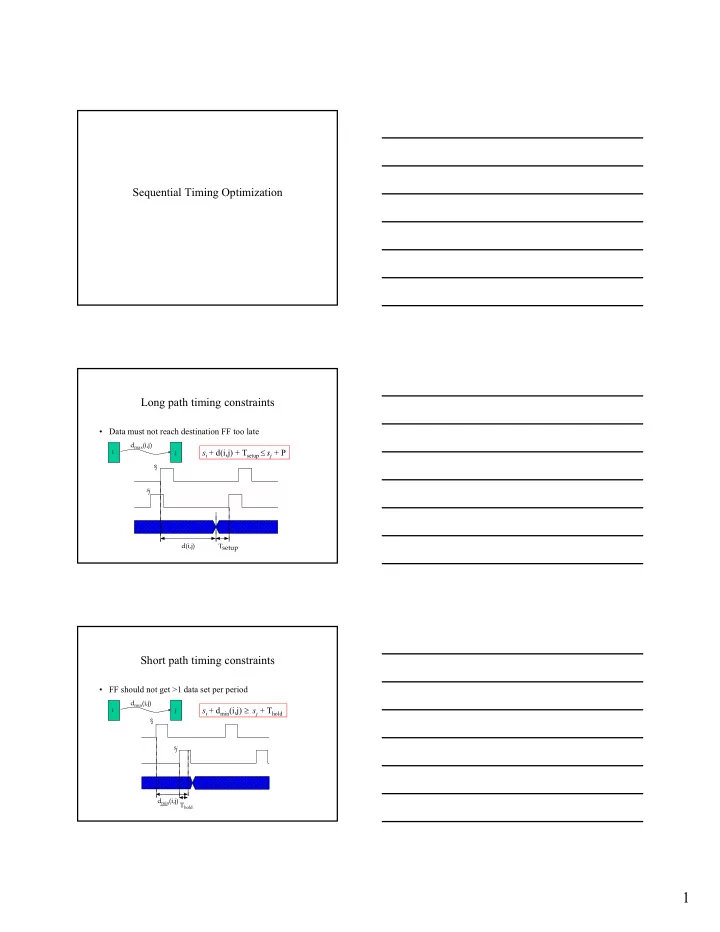

Constraints for retiming

- Non-negativity constraints (cannot have negative latencies)

– wr on each edge must be non-negative – For any edge from vertex u to vertex v, wr(u,v) = w(u,v) + r(v) – r(u) 0 wr(u,v) w(u,v) r(v) r(u) 0 i.e., r(u) – r(v) w(u,v)

- Period constraints (need a latency if path delay period)

– (or more precisely, path delay + Tsetup period) – For any path from vertex v1 to vertex vk, under clock period P, wr(v1 to vk) = w(v1 to vk) + r(vk) – r(v1) 1 if delay(v1 to vk) > P i.e., r(v1) – r(vk) w(v1 to vk) – 1 if delay(v1 to vk) > P