- v

- rdination

- f

- ard

- ptical

- v

- f

- nsible

- th

- do

- HTR

- rkhorse

- DCC

- rk.

- HR

- nsible

- n

- ard

- f

- n

- ptical

- ssibly

- f

- f

- m

- f

- ssibly

- ssibly

- f

0.1 CMS HCAL T rigger and Readout Electronics Pro ject The - - PDF document

0.1 CMS HCAL T rigger and Readout Electronics Pro ject The o v erall tec hnical co ordination for the HCAL trigger and readout electronics (T ri- D AS) pro ject will b e lo cated in the Maryland HEP group,

T T C 16 16 16 16

(2 channels/fiber)

HP G-Links: 16 bits data 20 bit frames 40 Mframe/sec

2 1

Ch A data Ch B data 7 7 Ch A data 9 1 Frame bit

Beam Crossing Fiber Input Ch B data 9 Beam Crossing Cap bits

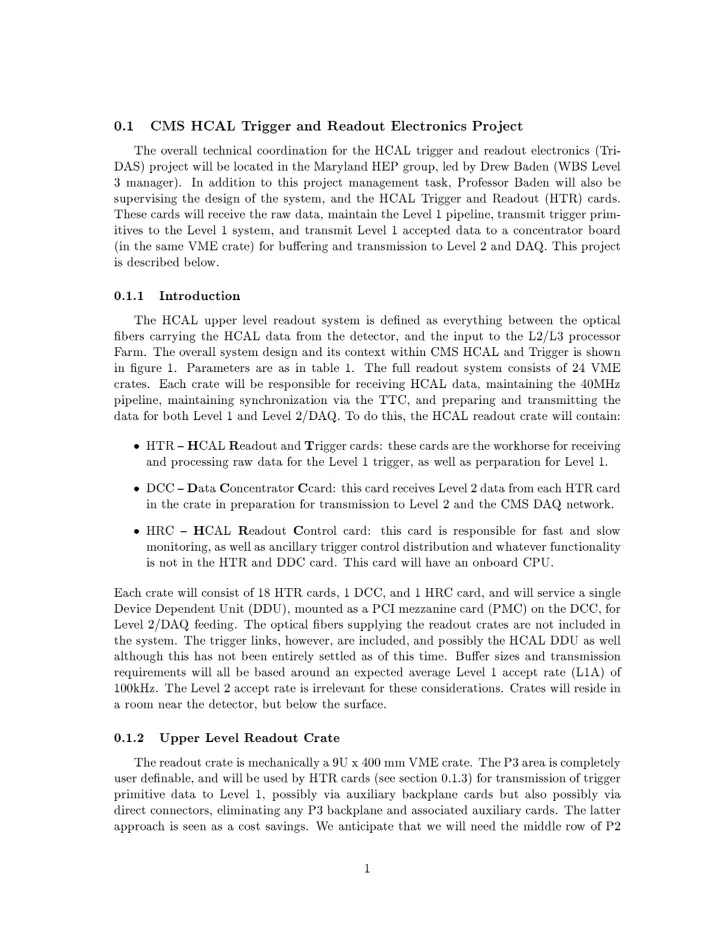

Figure 3: HTR input section. the single b eam crossing whic h created the energy . The MCM con tains a simple pro cessor for this purp24

Ch1A data Ch1A error 9 1 Ch2A data Ch2A error 9 1 ChA data 17 ChA data 16

16 1

Ch1B data Ch1B error 9 1 Ch2B data Ch2B error 9 1 ChB data 17 ChB data 16

Feature bit 1 Feature bit

Beam Crossing histogramming to check bunch structure

10 8

16

10 8 8 bits tower1 ET 1 feature bit tower1 8 bits tower2 ET 1 feature bit tower2 5 bits Hamming 1 abort gap flag Beam Crossing

16 16 16 16

Figure 4: HTR Lev el 1 P ath. As men tioned ab9+1 deRandomizing buffers 9+1 L2 Xmit Control

("SUM"s are calculated here)

Consists of16-bit words:

Header: Event ID (1) Beam crossing/"data state" (1) Data: Data buckets (N 10) SUM from filter (1) Address/error (1)

16

16 DCC

Ch data Ch error 9 1

Ch data Ch error 9 1

N•(9+1 bits)

Level 1 Accepts

32 channels total 9+1

N•(9+1 bits)

L1A decoder

Level 1 Framework L1A

Address pointer

"N" data buckets

12 bits

Beam Crossings 12

Beam Crossing

Linearizer 16+1 Linearizer 16+1

Tx

9+1 12

Figure 5: HTR Lev el 2/D A Q P ath. 0.1.4 Derandomizing Buer 0.1.5 Lev el 2 Filtering As discussed ab