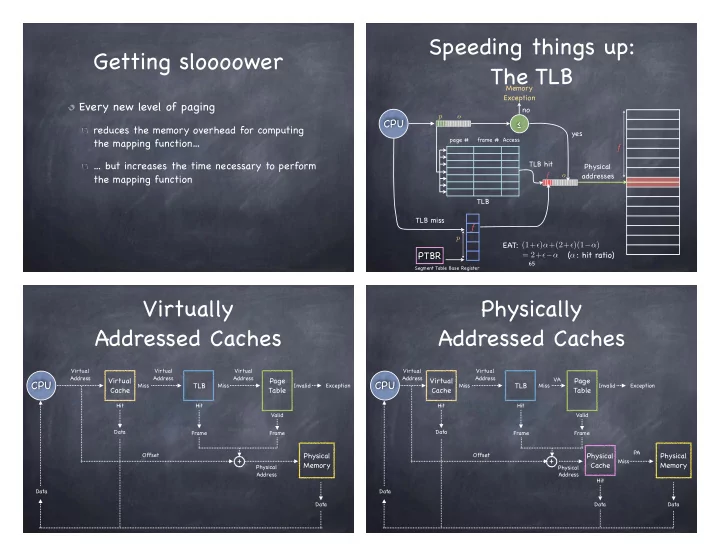

Getting sloooower

Every new level of paging

reduces the memory overhead for computing the mapping function… … but increases the time necessary to perform the mapping function

Speeding things up: The TLB

CPU

≤

yes Memory Exception Physical addresses

f

PTBR

- Segment Table Base Register

p f

f

p

- TLB miss

TLB hit

page # frame #

TLB no

EAT: (1+)α+(2+)(1−α) = 2+−α ( : hit ratio) α

65 Access

Virtually Addressed Caches

CPU

Virtual Cache Physical Memory TLB Page Table

Virtual Address Miss Virtual Address Miss

+

Invalid Exception Hit Hit Valid Frame Frame Physical Address Data Data Data Virtual Address Offset

Physically Addressed Caches

CPU

Virtual Cache Physical Memory TLB Page Table

Virtual Address Miss Virtual Address Miss

+

Invalid Exception Hit Hit Valid Frame Frame Physical Address Data Data Data VA

Physical Cache

PA Hit Data Miss Offset