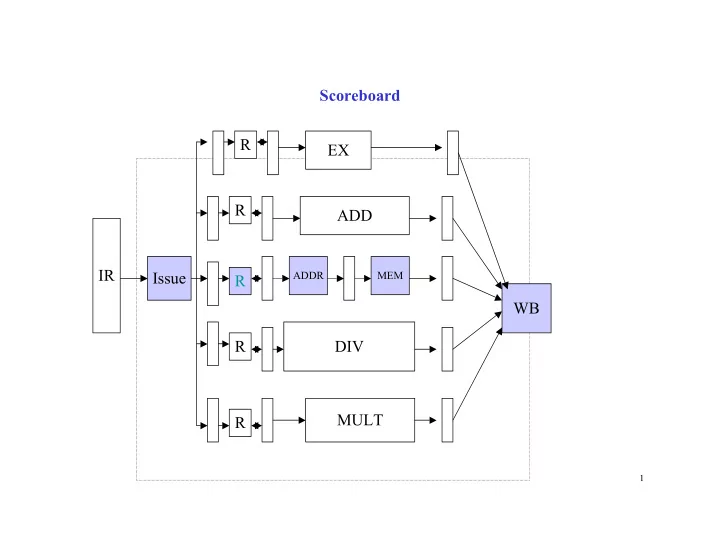

Scoreboard Issue ADD MULT DIV

MEM

IR R R R R WB

ADDR

EX R

1 1

Scoreboard R EX R ADD IR Issue ADDR MEM R WB R DIV MULT - - PowerPoint PPT Presentation

Scoreboard R EX R ADD IR Issue ADDR MEM R WB R DIV MULT R 1 1 Scoreboard Algorithm and Implementation Concentrate on Data Hazards only Array REGBusy[ ] one for each register Set to TRUE when an instruction that has that

1 1

2

3

4

5

6

7

8

9 9

10 10

11 11

12 12

13 13

14 14

15 15

16 16

17 17

C, D are SAFE-TO-WRITE; C, D are SAFE-TO-WRITE; F is not safe F is not safe Assume Assume C C is chosen to write; is chosen to write; Makes arrow out of F0 green. Makes arrow out of F0 green. E will read its operands in E will read its operands in second half of cycle second half of cycle

18 18 1 1

19 19

20 20

21 21

22 22

IF

IF I

IF I R

IF I R A

IF I R A M

IF I R R M W

I R R R W

R R + *

A R + *

M R + * 10 W R + *

W R W W

W / W

W /

/

/

W

WAR RAW RAW RAW STRUCT

STRUCT

23 23

24 24