1

- 3. Memory Management for

Embedded Systems

Embedded Operating Systems HPI

2

Roadmap for Section 3 Classical Memory Management Approaches - - PDF document

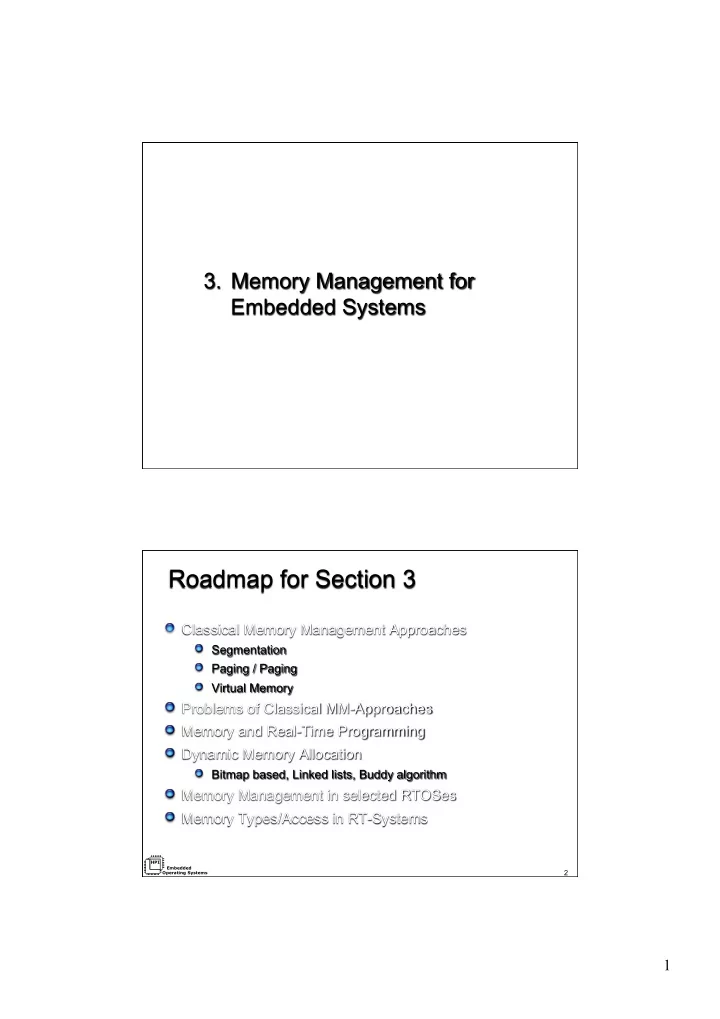

3. Memory Management for Embedded Systems Roadmap for Section 3 Classical Memory Management Approaches Segmentation Paging / Paging Virtual Memory Problems of Classical MM-Approaches Memory and Real-Time Programming

Embedded Operating Systems HPI

2

Embedded Operating Systems HPI

3

Embedded Operating Systems HPI

4

Embedded Operating Systems HPI

5

Embedded Operating Systems HPI

6

CPU s d

base

Physical memory Segment table logical address

limit

Addressing error

No Yes

Embedded Operating Systems HPI

7

base limit 1400 6300 4300 3200 4700 1000 400 400 1100 1000 1 2 3 4

segment 0 segment 3 segment 2 segment 4 segment 1

1400 2400 3200 4300 5700 6300 6700 4700

Segment table Physical memory

Embedded Operating Systems HPI

8

Embedded Operating Systems HPI

9

p d f d

f

p

logical address physical address page table

Embedded Operating Systems HPI

10

Embedded Operating Systems HPI

11

page 0 page 1 page 2 page n virtual memory memory map physical memory

Embedded Operating Systems HPI

12

Embedded Operating Systems HPI

13

Embedded Operating Systems HPI

14

Embedded Operating Systems HPI

15

Embedded Operating Systems HPI

16

Embedded Operating Systems HPI

17

Embedded Operating Systems HPI

18

Embedded Operating Systems HPI

19

Embedded Operating Systems HPI

20

Embedded Operating Systems HPI

21

Embedded Operating Systems HPI

22

Embedded Operating Systems HPI

23

Embedded Operating Systems HPI

24

Embedded Operating Systems HPI

25

Embedded Operating Systems HPI

26

Embedded Operating Systems HPI

27

Embedded Operating Systems HPI

28

Embedded Operating Systems HPI

29

Embedded Operating Systems HPI

30

Embedded Operating Systems HPI

31

Embedded Operating Systems HPI

32

Embedded Operating Systems HPI

33

Embedded Operating Systems HPI

34

Embedded Operating Systems HPI

35

Allocation

Acquire(Counting_Semaphore) Lock(mutex) Retrieve the memory block from the pool Unlock(mutex)

Deallocation

Lock(mutex) Release the memory block back to into the pool Unlock(mutex) Release(Counting_Semaphore)

Embedded Operating Systems HPI

36

Embedded Operating Systems HPI

37

Embedded Operating Systems HPI

38

Embedded Operating Systems HPI

39

Embedded Operating Systems HPI

40

Embedded Operating Systems HPI

41

INT i; PVOID pMem[512]; for (i = 0; i < 512; i++) { pMem[i] = VirtualAlloc (0, PAGE_SIZE, MEM_RESERVE | MEM_COMMIT, PAGE_READWRITE); } INT i; PVOID pBase, pMem[512]; pBase = VirtualAlloc (0, 512*PAGE_SIZE, MEM_RESERVE, PAGE_READWRITE); for (i = 0; i < 512; i++) { pMem[i] = VirtualAlloc (pBase + (i * PAGE_SIZE), PAGE_SIZE, MEM_COMMIT, PAGE_READWRITE); }

Embedded Operating Systems HPI

42

Embedded Operating Systems HPI

43

Embedded Operating Systems HPI

44

Embedded Operating Systems HPI

45

PC

address address data data

PC

address data

Embedded Operating Systems HPI

46

CPU

Cache Controller

Cache Main Memory

Data Data Address

CPU Main Memory L1 Cache L2 Cache

Embedded Operating Systems HPI

47

Embedded Operating Systems HPI

48

Embedded Operating Systems HPI

49

Embedded Operating Systems HPI

50

Embedded Operating Systems HPI

51

RAM ROM Flash

Address Bus Data Bus

EEPROM

0x00000000h 0x10000000h 0x20000000h 0x30000000h ROM

Flash

RAM

EEPROM

Embedded Operating Systems HPI

52

Embedded Operating Systems HPI

53

Embedded Operating Systems HPI

54

Embedded Operating Systems HPI

55

Embedded Operating Systems HPI

56

Procedure ZERO-ONE { 1: write 0 in all cells; 2: read all cells; 3: write 1 in all cells; 4: read all cells; }

Embedded Operating Systems HPI

57

Procedure Checkerboard { while(i is odd && j is even) { write 0 in cell[i]; write 1 in cell[j]; pause; read all cells; complement all cells; pause; read all cells; } }

Embedded Operating Systems HPI

58

Embedded Operating Systems HPI

59

Procedure GALPAT { write 0 in all cells; 2: for BC = 0 to N-1 { complement cell[BC]; for OC = 1 to n, BC != OC { read BC; read OC;} complement cell[BC]; } 3: write 1 in all cells; 4: replay Step 2; }

Embedded Operating Systems HPI

60

Embedded Operating Systems HPI

61