Chapter 2 <99>

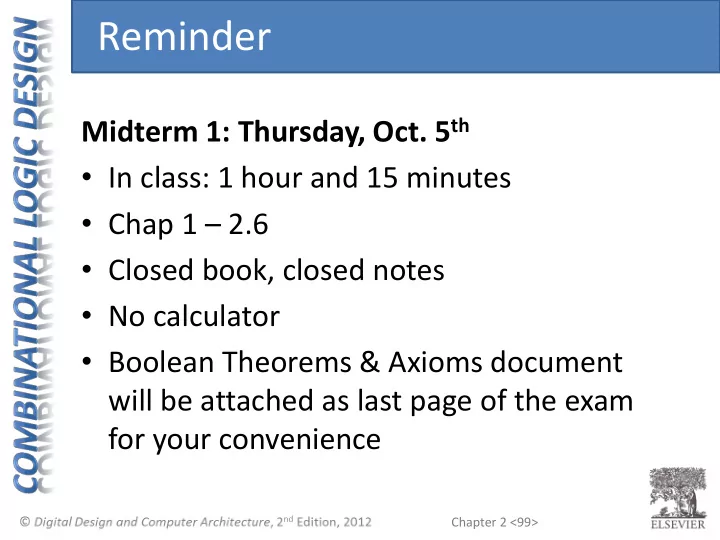

Midterm 1: Thursday, Oct. 5th

- In class: 1 hour and 15 minutes

- Chap 1 – 2.6

- Closed book, closed notes

- No calculator

- Boolean Theorems & Axioms document

Reminder Midterm 1: Thursday, Oct. 5 th In class: 1 hour and 15 - - PowerPoint PPT Presentation

Reminder Midterm 1: Thursday, Oct. 5 th In class: 1 hour and 15 minutes Chap 1 2.6 Closed book, closed notes No calculator Boolean Theorems & Axioms document will be attached as last page of the exam for your

Chapter 2 <99>

Chapter 2 <100>

Chapter 2 <101>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z)

Chapter 2 <102>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z) Make: X = (C+D+E), Z = B and rewrite equation Y = (A+X)(A+Z) substitution (X=(C+D+E), Z=B) = A + XZ T8’: Distributivity = A + (C+D+E)B substitution = A + BC + BD + BE T8: Distributivity

Y = AA+AB+AC+BC+AD+BD+AE+BE T8: Distributivity = A+AB+AC+AD+AE+BC+BD+BE T3: Idempotency = A + BC + BD + BE T9’: Covering

Chapter 2 <103>

O + C O C E 1 1 1 1 1 maxterm O + C O + C O + C

Chapter 2 <104>

Chapter 2 <105>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z)

Chapter 2 <106>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z) Make: X = B’C, Z = DE and rewrite equation Y = (A+XZ) substitution (X=B’C, Z=DE) = (A+B’C)(A+DE) T8’: Distributivity = (A+B’)(A+C)(A+D)(A+E) T8’: Distributivity

Chapter 2 <107>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z)

Chapter 2 <108>

Apply T8’ first when possible: W+XZ = (W+X)(W+Z) Make: W = AB, X = C’, Z = DE and rewrite equation Y = (W+XZ) + F substitution W = AB, X = C’, Z = DE = (W+X)(W+Z) + F T8’: Distributivity = (AB+C’)(AB+DE)+F substitution = (A+C’)(B+C’)(AB+D)(AB+E)+F T8’: Distributivity = (A+C’)(B+C’)(A+D)(B+D)(A+E)(B+E)+F T8’: Distributivity = (A+C’+F)(B+C’+F)(A+D+F)(B+D+F)(A+E+F)(B+E+F) T8’: Distributivity

Chapter 2 <109>

# Theorem Dual Name T6 B•C = C•B B+C = C+B Commutativity T7 (B•C) • D = B • (C•D) (B + C) + D = B + (C + D) Associativity T8 B • (C + D) = (B•C) + (B•D) B + (C•D) = (B+C) (B+D) Distributivity T9 B • (B+C) = B B + (B•C) = B Covering T10 (B•C) + (B•C) = B (B+C) • (B+C) = B Combining T11 (B•C) + (B•D) + (C•D) = (B•C) + (B•D) (B+C) • (B+D) • (C+D) = (B+C) • (B+D) Consensus Axioms and theorems are useful for simplifying equations.

Chapter 2 <110>

B (C+D) = BC + BD B + CD = (B+ C)(B+D)

A + AP = A

PA + PA = P

P = PA + PA A = A + AP

A = A + A

PA + A = P + A

Chapter 2 <111>

Chapter 2 <112>

Chapter 2 <113>

Chapter 2 <114>

Chapter 2 <115>

Chapter 2 <116>

A B Y A B Y A B Y A B Y

Chapter 2 <117>

Chapter 2 <118>

Chapter 2 <119>

Chapter 2 <120>

Chapter 2 <121>

– Body changes – Adds bubbles to inputs

– Body changes – Adds bubble to output

Chapter 2 <122>

Chapter 2 <123>

Chapter 2 <124>

Chapter 2 <125>

A B C Y D

Chapter 2 <126>

A B C Y D no output bubble

Chapter 2 <127>

bubble on input and output A B C D Y A B C Y D no output bubble

Chapter 2 <128>

A B C D Y bubble on input and output A B C D Y A B C Y D Y = ABC + D no output bubble no bubble on input and output

Chapter 2 <129>

O + C O C E 1 1 1 1 1 maxterm O + C O + C O + C

Chapter 2 <130>

B A C Y minterm: ABC minterm: ABC minterm: ABC A B C

Chapter 2 <131>

𝑍 = 𝐶 𝐷 + 𝐵𝐶

Chapter 2 <132>

wires connect at a T junction wires connect at a dot wires crossing without a dot do not connect

Chapter 2 <133>

A1 A 1 1 1 1 Y3 Y2 Y1 Y0 A

3

A2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 A0 A1 PRIORITY CiIRCUIT A2 A3 Y0 Y1 Y2 Y3

Chapter 2 <134>

A1 A 1 1 1 1 Y3 Y2 Y1 Y0 1 1 1 A

3

A2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 A0 A1 PRIORITY CiIRCUIT A2 A3 Y0 Y1 Y2 Y3

Chapter 2 <135>

A1 A 1 1 1 1 Y3 Y2 Y1 Y0 1 1 1 A

3

A2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Chapter 2 <136>

A1 A 1 1 1 1 Y3 Y2 Y1 Y0 1 1 1 A

3

A2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

A1 A0 1 1 X X X Y3 Y2 Y1 Y0 1 1 1 A3 A2 1 X X 1 1 X

A3A2A1A0 Y3 Y2 Y1 Y0

Much easier to read off Boolean equations = 𝐵3 = 𝐵3𝐵2 = 𝐵3 𝐵2 𝐵1 = 𝐵3 𝐵2 𝐵1 𝐵0

Chapter 2 <137>

– Actual value somewhere in between – Could be 0, 1, or in forbidden zone – Might change with voltage, temperature, time, noise – Often causes excessive power dissipation

– Contention usually indicates a bug. – X is used for “don’t care” and contention - look at the context to tell them apart

Chapter 2 <138>

E A Y Z 1 Z 1 1 1 1 A E Y

Note: tristate buffer has an enable bit (𝐹) to turn

Chapter 2 <139>

en1 to bus from bus en2 to bus from bus en3 to bus from bus en4 to bus from bus

shared bus processor video Ethernet memory