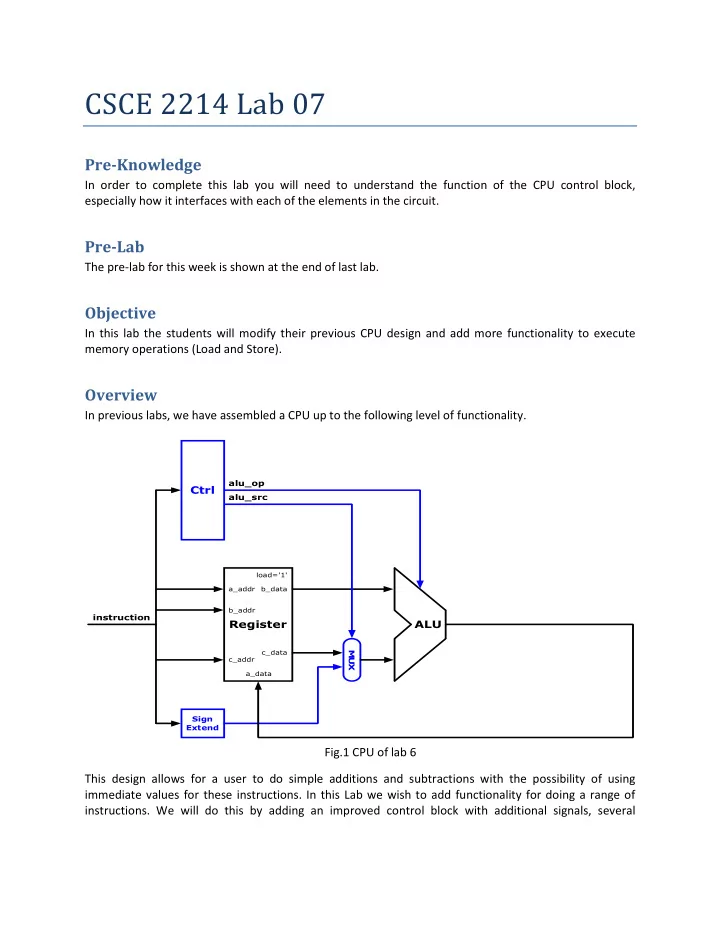

SLIDE 5 The above figure is the final goal of this assignment. Some of the components are given to you as additional materials. It is your responsibility to implement the rest of the design. The test bench for this lab is provided in Table 1.

Control Unit: In this lab, the previous control unit will be modified to add more instructions. The op

code value is still 4 bits long and the corresponding instruction (to be used in this lab) is given in the table below : Opcode(Binary) Operation 0000 ADD 0001 SUB 0010 AND 0011 OR 0100 ADDI 0101 SUBI 1000 LW 1100 SW The following interface could be used to implement the control block: Entity Control is Port(

: in std_logic_vector( 3 downto 0); alu_op :

std_logic_vector( 1 downto 0); alu_src :

std_logic; reg_dest :

std_logic; reg_load :

std_logic; reg_src :

std_logic_vector(1 downto 0); mem_read :

std_logic; mem_write :

std_logic

); End control; e.g: In case of a SW Rd, off(Rs) instruction (opcode 1100), we will have the following configuration:

alu_op = 0 => The offset will be added to the Rs address to compute the location where to store the Rd value inside the data memory. alu_src = 1 => Since the second operand of SW is an offset (integer), the output of the signExtend unit must be selected. reg_dest = 1 => Since the input address for c_addr should be Rd, this value is therefore set to 1. reg_load = 0 => No value is saved in the Register file. reg_src = 1 => The output of the ALU is the location where Rd has been saved in the Data memory. Setting reg_src to 1 allows us to monitor the value of that memory location. mem_read = 0 => This is not a memory read operation mem_write = 1 => Rd value is saved in the data memory. It’s therefore a memory write.