SLIDE 1

Optimization (Karnaugh maps) a b c d e 0 0 0 0 0 0 0 0 - - PowerPoint PPT Presentation

Optimization (Karnaugh maps) a b c d e 0 0 0 0 0 0 0 0 - - PowerPoint PPT Presentation

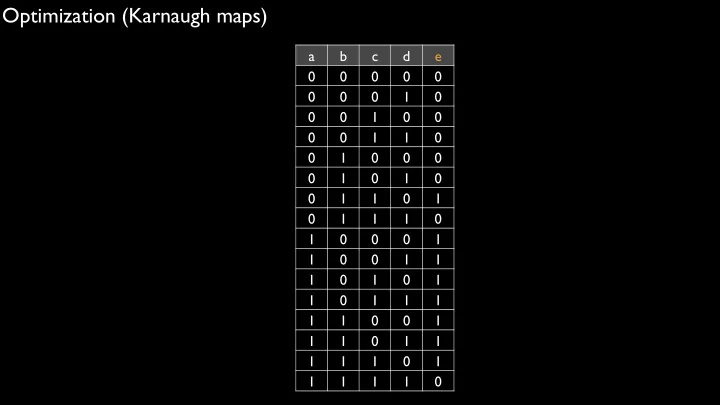

Optimization (Karnaugh maps) a b c d e 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0

SLIDE 2

SLIDE 3

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’

Optimization (Karnaugh maps)

SLIDE 4

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’

Optimization (Karnaugh maps)

SLIDE 5

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’ a . b’ . c’ . d

Optimization (Karnaugh maps)

SLIDE 6

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’ a . b’ . c’ . d a . b’ . c . d’

Optimization (Karnaugh maps)

SLIDE 7

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’ a . b’ . c’ . d a . b’ . c . d’ a . b’ . c . d a . b . c’ . d’ a . b . c’ . d a . b . c . d’

Optimization (Karnaugh maps)

SLIDE 8

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’ a . b’ . c’ . d a . b’ . c . d’ a . b’ . c . d a . b . c’ . d’ a . b . c’ . d a . b . c . d’}

- r

Optimization (Karnaugh maps)

SLIDE 9

00 01 11 10 00 01 11 10 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 10

00 01 11 10 00 01 11 10 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 11

00 01 11 10 00 1 01 11 10 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 12

00 01 11 10 00 1 01 11 10 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 13

00 01 11 10 00 1 01 11 10 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 14

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 15

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 16

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a . b’

Optimization (Karnaugh maps)

SLIDE 17

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 18

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

b . c . d’

Optimization (Karnaugh maps)

SLIDE 19

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Optimization (Karnaugh maps)

SLIDE 20

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a . c’

Optimization (Karnaugh maps)

SLIDE 21

00 01 11 10 00 1 1 01 1 1 11 1 10 1 1 1 ab cd

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a . c’ b . c . d’ a . b’

e = + + Optimization (Karnaugh maps)

SLIDE 22

a b c d e 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

a’ . b . c . d’ a . b’ . c’ . d’ a . b’ . c’ . d a . b’ . c . d’ a . b’ . c . d a . b . c’ . d’ a . b . c’ . d a . b . c . d’

Optimization (Karnaugh maps)

SLIDE 23

Circuits A circuit is a collection of logical gates that transforms a set of binary inputs into a set of binary outputs.

SLIDE 24

+

a b c ⋅ d

input

- utput

Circuits

SLIDE 25

+

a b c ⋅ d

(a + b)

c = (a + b) Circuits

SLIDE 26

+

a b c ⋅ d

(a + b) (a + b) ⋅ b’ b’

Circuits

SLIDE 27

+

a b c ⋅ d

(a + b) (a + b) ⋅ b’ b’

d = ((a + b) ⋅ b’)’ Circuits

SLIDE 28

Designing Circuits

step 1. build truth-table for all possible input/output values

a b c d

1 1 1 1

input

- utput

SLIDE 29

step 1. build truth-table for all possible input/output values

a b c d

1 1 1 1 1 1 1

input

- utput

arbitrary, for now

Designing Circuits

SLIDE 30

step 2. build sub-expressions with and/not for each output column

a b c d

1 1 1 1 1 1 1

input

- utput

arbitrary, for now

Designing Circuits

SLIDE 31

step 2. build sub-expressions with and/not for each output column

a b c d

1 1 1 1 1 1 1

input

- utput

d = a ⋅ b Designing Circuits

SLIDE 32

step 2. build sub-expressions with and/not for each output column

a b c d

1 1 1 1 1 1 1

input

- utput

c = a’ ⋅ b Designing Circuits

SLIDE 33

step 2. build sub-expressions with and/not for each output column

a b c d

1 1 1 1 1 1 1

input

- utput

c = a’ ⋅ b c = a ⋅ b’ Designing Circuits

SLIDE 34

step 3. combine, two at a time, sub-expressions with an or

a b c d

1 1 1 1 1 1 1

input

- utput

Designing Circuits

SLIDE 35

step 3. combine, two at a time, sub-expressions with an or

a b c d

1 1 1 1 1 1 1

input

- utput

c = (a’ ⋅ b ) + (a ⋅ b’) Designing Circuits

SLIDE 36

step 3. combine, two at a time, sub-expressions with an or

a b c d

1 1 1 1 1 1 1

input

- utput

c = (a’ ⋅ b ) + (a ⋅ b’) d = a ⋅ b Designing Circuits

SLIDE 37

step 4. draw circuit diagram

d = a⋅b a b ⋅ d

(a⋅b)

Designing Circuits

SLIDE 38

step 4. draw circuit diagram

c = (a’⋅b) + (a⋅b’) +

a b c ⋅ d ⋅ ⋅

(a’⋅b) (a⋅b’)

Designing Circuits

SLIDE 39

step 4. draw circuit diagram

c = (a’⋅b ) + (a⋅b’)

a b ⋅ d

+

⋅ ⋅

(a’⋅b) (a⋅b’)

c Designing Circuits

SLIDE 40

step 1. build truth-table for all possible input/output values step 2. build sub-expressions with and/not for each output column step 3. combine, two at a time, sub-expressions with an or step 4. draw circuit diagram

Designing Circuits

SLIDE 41

1-Bit Compare for Equality (CE) If two bits a, b are equal then return 1 else return 0

SLIDE 42

a b c

1 1 1 1

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 43

a b c

1 1 1 1 1 1

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 44

a b c

sub- expression

1 1 1 1 1 1

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 45

a b c

sub- expression

1

a’ ⋅ b’

1 1 1 1 1

a ⋅ b

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 46

a b c

sub- expression

1

a’ ⋅ b’

1 1 1 1 1

a ⋅ b

input

- utput

c = (a’ ⋅ b’) + (a ⋅ b) 1-Bit Compare for Equality (CE)

SLIDE 47

a b c c = (a’ ⋅ b’) + (a ⋅ b)

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 48

a b c ⋅

(a ⋅ b)

c = (a’ ⋅ b’) + (a ⋅ b)

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 49

a b c ⋅

(a ⋅ b)

⋅

(a’ ⋅ b’)

c = (a’ ⋅ b’) + (a ⋅ b)

input

- utput

1-Bit Compare for Equality (CE)

SLIDE 50

a b c ⋅

(a ⋅ b)

⋅

(a’ ⋅ b’)

c = (a’ ⋅ b’) + (a ⋅ b)

input

- utput

+ (a’⋅b’)+(a⋅b)

1-Bit Compare for Equality (CE)

SLIDE 51

4-Bit Compare for Equality (CE) If two 4-bit numbers are equal then return 1 else return 0

SLIDE 52

If two 4-bit numbers are equal then return 1 else return 0 a3 a2 a1 a0 == b3 b2 b1 b0 4-Bit Compare for Equality (CE)

SLIDE 53

a3 a2 a1 a0 b3 b2 b1 b0

c

input

- utput

how many rows? 4-Bit Compare for Equality (CE)

SLIDE 54

256 4-Bit Compare for Equality (CE)

SLIDE 55

two 4-bit numbers are equal if: a3 == b3 and a2 == b2 and a1 == b1 and a0 == b0 a3 a2 a1 a0 == b3 b2 b1 b0 4-Bit Compare for Equality (CE)

SLIDE 56

a b c ⋅

(a ⋅ b)

⋅

(a’ ⋅ b’) + (a’⋅b’)+(a⋅b)

4-Bit Compare for Equality (CE)

SLIDE 57

a b c ⋅

(a ⋅ b)

⋅

(a’ ⋅ b’) + (a’⋅b’)+(a⋅b)

1-CE

a b c 4-Bit Compare for Equality (CE)

SLIDE 58

a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

c 4-Bit Compare for Equality (CE)

SLIDE 59

a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

1-CE

c 4-Bit Compare for Equality (CE)

SLIDE 60

a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

1-CE 1-CE 1-CE 1-CE

c 4-Bit Compare for Equality (CE)

SLIDE 61

c a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

1-CE 1-CE 1-CE 1-CE

⋅ 4-Bit Compare for Equality (CE)

SLIDE 62

c a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

1-CE 1-CE 1-CE 1-CE

⋅ ⋅ 4-Bit Compare for Equality (CE)

SLIDE 63

c a3 b3 a2 b2 a1 b1 a0 b0

input

- utput

1-CE 1-CE 1-CE 1-CE

⋅ ⋅ ⋅ 4-Bit Compare for Equality (CE)

SLIDE 64

1-Bit Adder build a circuit that adds two 1-bit numbers

SLIDE 65

0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = ? 1-Bit Adder

SLIDE 66

0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 need to carry 1-Bit Adder

SLIDE 67

0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 input: two digits a, b 1-Bit Adder

SLIDE 68

0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 input: two digits a, b and a carry c 1-Bit Adder

SLIDE 69

0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10

- utput: sum d and carry e

1-Bit Adder

SLIDE 70

101 001

- 5

1

- 6

22+20 20

1-Bit Adder

SLIDE 71

1 101 001

- 5

1

- 6

1-Bit Adder

SLIDE 72

1 101 001

- 10

5 1

- 6

1-Bit Adder

SLIDE 73

1 101 001

- 110

5 1

- 6

1-Bit Adder

SLIDE 74

1 101 001

- 110

5 1

- 6

22+21

1-Bit Adder

SLIDE 75

input: digits a, b and carry c

- utput: sum d and carry e

1-Bit Adder

SLIDE 76

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 77

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 78

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 79

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 80

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 81

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 82

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 83

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 84

input: digits a, b and carry c

- utput: sum d and carry e

a b c d e

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 85

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 86

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 87

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 88

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 89

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 1 1 a⋅b’⋅c’ 1 1 1 1 1 1 1 1 1 1 1

1-Bit Adder

SLIDE 90

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 1 1 a⋅b’⋅c’ 1 1 1 1 1 1 1 1 1 1 1 a⋅b⋅c

1-Bit Adder

SLIDE 91

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 a’⋅b⋅c 1 1 a⋅b’⋅c’ 1 1 1 a⋅b’⋅c 1 1 1 a⋅b⋅c’ 1 1 1 1 1 a⋅b⋅c a⋅b⋅c

1-Bit Adder

SLIDE 92

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 a’⋅b⋅c 1 1 a⋅b’⋅c’ 1 1 1 a⋅b’⋅c 1 1 1 a⋅b⋅c’ 1 1 1 1 1 a⋅b⋅c a⋅b⋅c d = (a’⋅b’⋅c) + (a’⋅b⋅c’) + (a⋅b’⋅c’) + (a⋅b⋅c)

1-Bit Adder

SLIDE 93

a b c d e

sub-expressions (d) sub-expressions (e)

1 1 a’⋅b’⋅c 1 1 a’⋅b⋅c’ 1 1 1 a’⋅b⋅c 1 1 a⋅b’⋅c’ 1 1 1 a⋅b’⋅c 1 1 1 a⋅b⋅c’ 1 1 1 1 1 a⋅b⋅c a⋅b⋅c e = (a’⋅b⋅c) + (a⋅b’⋅c) + (a⋅b⋅c’) + (a⋅b⋅c)

1-Bit Adder

SLIDE 94

a’⋅b’⋅c

a b c d e 1-Bit Adder

SLIDE 95

4-Bit Adder build a circuit that adds two 4-bit numbers

SLIDE 96

1-ADD

a b d c e

carry-in carry-out sum digits

4-Bit Adder

SLIDE 97

a0 a1 a2 a3 b0 b1 b2 b3

1-ADD

d0 c0 4-Bit Adder

SLIDE 98

a0 a1 a2 a3 b0 b1 b2 b3

1-ADD

d0 c0 4-Bit Adder

SLIDE 99

a0 a1 a2 a3 b0 b1 b2 b3

1-ADD 1-ADD

d0 c0 d1 c1 4-Bit Adder

SLIDE 100

a0 a1 a2 a3 b0 b1 b2 b3

1-ADD 1-ADD 1-ADD

d0 c0 d1 c1 d2 c2 4-Bit Adder

SLIDE 101

a0 a1 a2 a3 b0 b1 b2 b3

1-ADD 1-ADD 1-ADD 1-ADD

d0 c0 d1 c1 d2 c2 d3 4-Bit Adder

SLIDE 102

32-bit Adder 96 = 32x3 not gates 512 = 32x16 and gates 192 = 32x6 or gates 800 gates

SLIDE 103

96 = 32x3 not gates 512 = 32x16 and gates 192 = 32x6 or gates 800 gates 1,504 = 96+1024+384 transistors 32-bit Adder

SLIDE 104

96 = 32x3 not gates 512 = 32x16 and gates 192 = 32x6 or gates 800 gates 1,504 = 96+1024+384 transistors 1945: refrigerator-sized computer 2015: .-sized computer 32-bit Adder

SLIDE 105

Equals 0 build a circuit that determines if an 8-bit number is 0

SLIDE 106

a7 a6 a5 a4 a3 a2 a1 a0 = 00000000 Equals 0

SLIDE 107

a b c d e f g h

i

How many rows? . . . . . .

- utput

Equals 0

SLIDE 108

a b c d e f g h

i

1

Only one row has an output of 1 Equals 0

SLIDE 109

a b c d e f g h

i

1

i = a’ ⋅ b’ ⋅ c’ ⋅ d’ ⋅ e’ ⋅ f’ ⋅ g’ ⋅ h’ Equals 0

SLIDE 110

a b c d e f g h i Equals 0

SLIDE 111

a b c d e f g h ⋅ i ⋅ ⋅ ⋅ Equals 0

SLIDE 112

a b c d e f g h ⋅ i ⋅ ⋅ ⋅ ⋅ ⋅ Equals 0

SLIDE 113