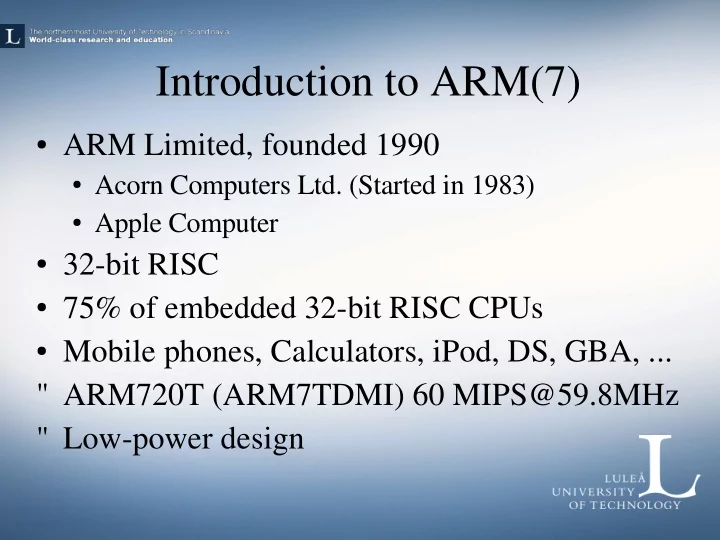

Introduction to ARM(7)

- ARM Limited, founded 1990

- Acorn Computers Ltd. (Started in 1983)

- Apple Computer

- 32-bit RISC

- 75% of embedded 32-bit RISC CPUs

- Mobile phones, Calculators, iPod, DS, GBA, ...

Introduction to ARM(7) ARM Limited, founded 1990 Acorn Computers - - PowerPoint PPT Presentation

Introduction to ARM(7) ARM Limited, founded 1990 Acorn Computers Ltd. (Started in 1983) Apple Computer 32-bit RISC 75% of embedded 32-bit RISC CPUs Mobile phones, Calculators, iPod, DS, GBA, ... " ARM720T (ARM7TDMI) 60

// Get user mode sp stmfd sp!, {r0} stmdb sp, {sp}^ nop ldmdb sp, {r0} // Store return address sub lr, lr, #4 stmfd r0!, {lr} // Start using lr mov lr, r0 ldmfd sp!, {r0} // Save user mode regs stmfd lr, {r0-r14}^ nop sub lr, lr, #60 // Save SPSR. mrs r0, SPSR stmfd lr!, {r0} // Save stack pointer ldr r0, =tt_current ldr r0, [r0] str lr, [r0]

// Restore user mode regs ldmfd lr, {r0, r14} nop add lr, lr, #60 // Return from interrupt ldmfd lr, {pc}^ // Load sp ldr r0, =tt_current ldr r0, [r0] ldr lr, [r0] // Restore SPSR ldmfd lr!, {r0} msr r0, SPSR

// Save user regs. subu $29, $29, 116 sw $1, 0($29) . . . sw $31, 108($29) // Save return address mfc0 $26, $14 nop sw $26, 112($29) // Save sp la $1, tt_current lw $1, 0($1) nop sw $29, 0($1) nop

// Restore return addr lw $26, 112($29) addu $29, $29, 116 // Return from interrupt jr $26 rfe // Load sp la $29, tt_current lw $29, 0($29) nop lw $29, 0($29) nop // Restore user regs lw $1, 0($29) . . . lw $31, 108($29)