I njection Velocity in Thin-Channel I nAs HEMTs Tae-Woo Kim and - PowerPoint PPT Presentation

I njection Velocity in Thin-Channel I nAs HEMTs Tae-Woo Kim and Jess A. del Alamo Microsystems Technology Laboratories MIT IPRM Sponsors: Intel, FCRP-MSD May 24 th , 2011 Fabrication: MTL, NSL, SEBL at MIT Acknowledgement: Dae-Hyun Kim

I njection Velocity in Thin-Channel I nAs HEMTs Tae-Woo Kim and Jesús A. del Alamo Microsystems Technology Laboratories MIT IPRM Sponsors: Intel, FCRP-MSD May 24 th , 2011 Fabrication: MTL, NSL, SEBL at MIT Acknowledgement: Dae-Hyun Kim (Teledyne Scientific) 1

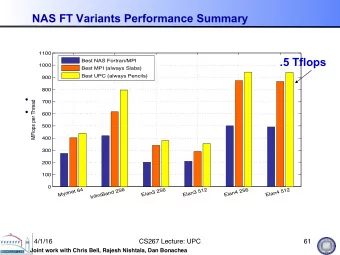

I njection Velocity in I I I -V QW FETs • Injection velocity: average velocity of electrons at virtual source - sets I ON which determines switching speed • Recent measurements of v inj in InAs HEMTs: 2 /V-s n ~ 13,000 cm 4 V DS = 0.5 V v inj InAs, t ch = 10 nm E C 3 >2X 7 cm/s] higher E V 2 at half V DD v inj [10 1 *Strain-Si *Si nFETs Kim, IEDM 2009 (V DS = 1.1 ~ 1.3 V) 0 10 100 L g [nm] • v inj (InAs) > 2 v inj (Si) at less than half V DD • Derived v inj values consistent with purely ballistic transport 2

Role of channel thickness in QW-FET scalability 90 160 In 0.7 Ga 0.3 As HEMT: t ch = 13 nm Subtreshold swing [mV/dec] In 0.7 Ga 0.3 As HEMTs: t ch = 13 nm 80 120 DIBL [mV/V] InAs HEMTs: InAs HEMTs: t ch = 10 nm t ch = 10 nm 70 80 InAs HEMTs: t ch = 5 nm InAs HEMTs: t ch = 5 nm 60 40 40 80 120 160 200 40 80 120 160 200 L g [nm] L g [nm] Kim, IPRM 2010 • Dramatic improvement in short-channel effects in thin-channel devices • Concern: v inj degradation in thin-channel devices? 3

Extraction methodology for v inj v inj = I D I D = Q i_x0 v inj Q i_x0 V G V G V S V S V D V D - I D : measured drain current I D I D - Q i_x0 : sheet-charge density R D R D R S R S Q i_x0 = C gi dV GS,i Q i_x0 Q i_x0 with C gi @ V DS = 10 mV v x0 v x0 E C E C - C gi extracted from S-parameters inj - R S and R D correction: V DSi = V DS – I D (R S + R D ) x x 0 0 L L V GSi = V GS – I D R S x o x o - V T roll-off correction Kim, IEDM 2009 - DIBL correction 4

Thin-channel I nAs HEMTs Kim, IPRM 2010 S D L g ~ 40 nm Oxide L side InGaAs/InAlAs t ch = 5 nm t ins = 7 nm 6 nm InP L g 11 nm In 0.52 Al 0.48 As t ins In 0.7 Ga 0.3 As: 1 nm t ch InAs: 2 nm t ch = 5 nm In 0.7 Ga 0.3 As: 2 nm n,Hall = 9,950 cm 2 /V-sec Buffer : In 0.52 Al 0.48 As • Triple-step gate recess process Reference: • Gate metal stack: Ti/Pt/Au • InAs HEMT with t ch = 10 nm n,Hall = 13,500 cm 2 /V-sec • L g = 40 ~ 200 nm • • L side = 80 nm, t ins = 3, 7 nm Kim, IEDM 2008 5

I -V Characteristics: L g = 40 nm with t ins = 3 nm • V T = 0.11 V, S = 65 mV/dec, DIBL = 50 mV/V g m =1.6 mS/ m, R S =275 Ohm- m • 6

Extraction of Q i_x0 • C gi extracted from S-parameters @ V DS = 10 mV • Parasitic capacitance removed Q i_x0 = C gi dV GS,i • V DS = 10 mV 7

v inj of L g = 40 nm t ins = 3 nm I nAs HEMTs 4 V DS = 0.5 V v inj =3.3x10 7 cm/s @ 0.5 V 3 7 cm/s] V DS = 0.4 V 2 inj [10 V DS = 0.3 V 1 V DS = 0.1 V tins = 3 nm 0 0.0 0.1 0.2 0.3 0.4 V GSi - V T [v] V DS v inj (device driven into saturation) • V GSi -V T v inj initially (because Q i_xo ) • then v inj (device driven into linear regime) 8

v inj vs. L g 4 L g = 40 nm L g = 70 nm 3 7 cm/s] L g = 100 nm L g = 150 nm 2 v inj [10 L g = 200 nm 1 t ins = 3 nm, V DS = 0.5 V 0 0.0 0.1 0.2 0.3 0.4 V GSi - V T [v] L g v inj 9

v inj - impact of channel thickness 4 VDS = 0.5 V 2 /V-s n ~ 13,000 cm t ins = 4 nm & t ch = 10 nm 2 /V-s n ~ 9,950 cm 3 Kim, IEDM 2009 t ins = 3 nm & t ch = 5 nm 7 cm/s] 2 v inj [10 1 Strain-Si Si nFETs (VDS = 1.1 ~ 1.3 V) 0 10 100 L g [nm] In thin-channel devices: Long L g : v inj decreases right along with e (~23%) • • Short L g : v inj relatively unaffected consistent with ballistic transport 10

Conclusions • Thin-channel InAs HEMTs with t ch =5 nm: - Evidence of mobility degradation - Small degradation in injection velocity for short L g FETs: v inj = 3.3 10 7 cm/s at L g = 40 nm • Great scaling potential of thin-channel FETs • Key question: - Can v inj be preserved if severe degradation (~3000 cm 2 /V.s)? 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.