2012-05-22

- E. Hazen -- Upgrade Week

2

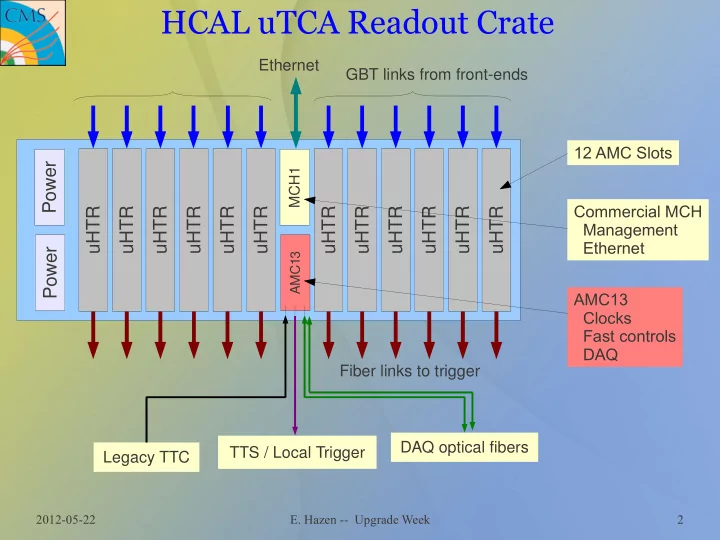

HCAL uTCA Readout Crate

uHTR uHTR uHTR uHTR uHTR uHTR uHTR uHTR uHTR uHTR uHTR uHTR

TTS / Local Trigger GBT links from front-ends Fiber links to trigger

M C H 1

Ethernet

AMC13

Power Power

Legacy TTC DAQ optical fibers 12 AMC Slots Commercial MCH Management Ethernet AMC13 Clocks Fast controls DAQ