SLIDE 4 Status

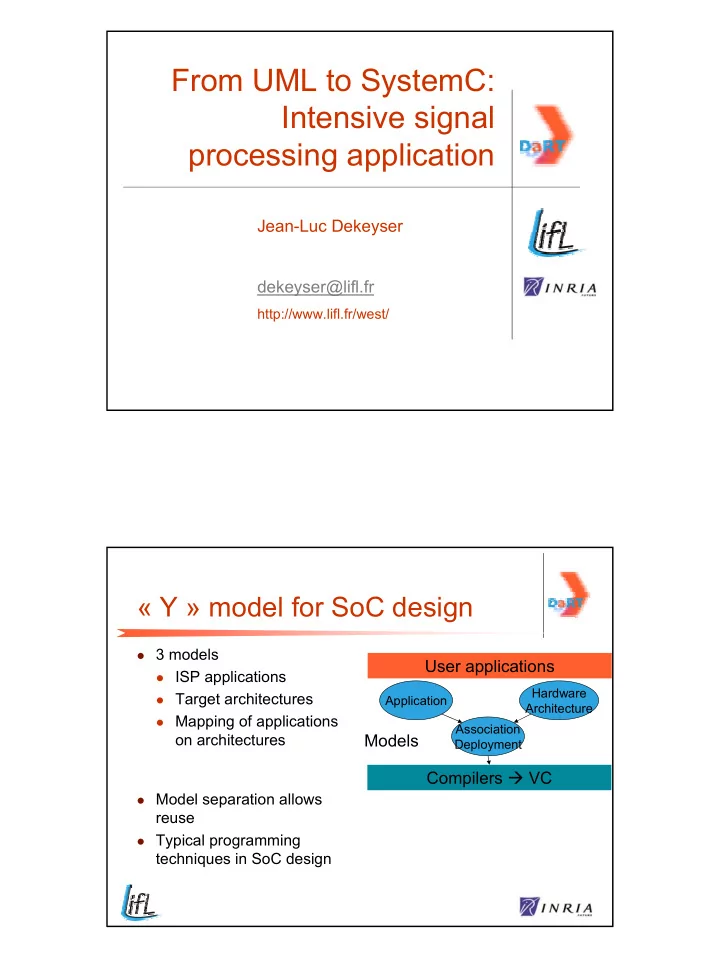

Visual modeling of Intensive Signal Processing Application Eclpis Plugin Metamodel and UML profile of ISP Model to model transformation and code generation

- UML TAU G2 <-> ISP

- ISP -> SystemC

ISP domain in SystemC ( KPN execution model) Distributed SystemC runtime

Multi abstraction level SystemC simulation

Application PIM: ISP Example

hydro hydro

fft : FFT fft : FFT

input1 input1

fv : FV fv : FV

input1 input1 result result coeff coeff

norm : Normalization norm : Normalization

input1 input1 result result

lbl : LargeBandRegroup lbl : LargeBandRegroup

input1 input1 result result

shortIntegration : Integration shortIntegration : Integration

input1 input1 result result

azimutStabilization : AzimutStabilization azimutStabilization : AzimutStabilization

input1 input1 input2 input2 result result

longIntegration : Integration longIntegration : Integration

input1 input1 result result coeffAz coeffAz result result coeffV coeffV input1 input1

fft : etFFT fft : etFFT

input1 input1 result result

<<aolTiler>>

qd1 : AolTiler

<<aolTiler>>

qd1 : AolTiler

array array pattern pattern

<<aolTiler>>

qd2 : AolTiler

<<aolTiler>>

qd2 : AolTiler

array array pattern pattern